|

CADENCE-SiP 对射频模拟设计的技术支持

RF-PCB版图形状的处理

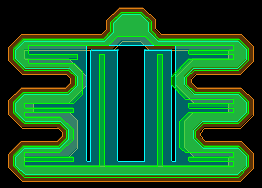

CADENCE RF-PCB在射频电路中铜皮的编辑处理方面具有突出优势:

特色

1) 支持分立器件与微波线路连接点的平滑过渡处理;

2) 支持铜皮转角的弧形处理或切角处理;

3) 支持天线间微波线路波长的自动计算与绕线;

4) 支持不同层间铜皮自动转化成独立的器件;

5) 支持灵活的铜皮间避让与合并的处理功能;

6) 支持对微波线路的自动计算波长和打过孔屏蔽功能。

1. 腔体设计的支持

针对所里面设计项目的特殊性和对小型化的迫切需求,该项功能可以很好的解决目前项目中碰到的一些问题。

特色

1)叠层芯片可以沉降到基板的任何层上,灵活的调节芯片叠层位置和高度

2) 有效减少金线的延展长度,降低生产成本,提高BONDING工艺的可靠性和产品良率。

3) 支持芯片任意角度的旋转,在设计中具有非常高的灵活性。

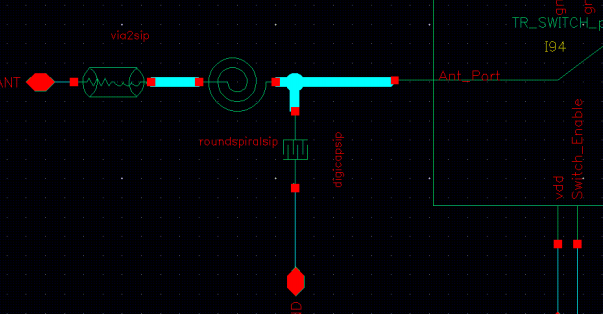

2. 埋入式无源器件,参数化单元

针对目前项目,在RF模块设计工具中将会需要用到RF IC设计中认可的一些功能。例如,基板级RF无源器件的参数化设计单元(P-Cells)在定制IC工具中是标配,而在如今领先的封装设计工具中却是不存在的,Cadence技术将他们引入成为所有SiP解决方案的一部分。

特色

1) 支持原理图阶段就引用和编辑无源PCELL器件并带入到仿真过程中

2) 并内嵌场解算器,实时计算并给出PCELL的各项指标随参数的变化特性

3) 支持SIP-LAYOUT中修改调整PCELL器件的具体参数以达到设计的目标

4) 支持SIP-LAYOUT中修改反标回原理图

5) 提供扩展二次开发接口,用户可以根据自己的设计需要重新定制、生成和编辑新的PCELL

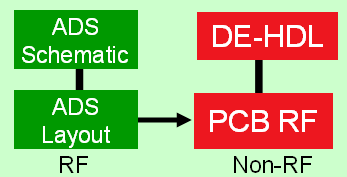

3. 支持多种与ADS工具的接口

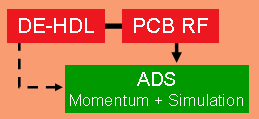

方式一:射频设计采用ADS,非射频电路设计采用Cadence设计,最终RF模块导入Cadence中合成PCB的设计流程

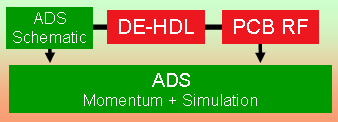

方式二:电路设计过程全部由Cadence完成, ADS仅负责完成射频电路分析

方式三:ADS与Cadence结合的方式完成电路设计,这样在原理图设计阶段即可预分析电路的基本功能

4. 与HFSS分析工具的接口

特色

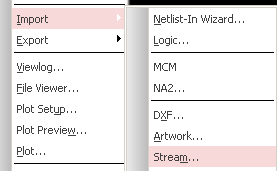

1) Cadence与HFSS通过gds格式文件将各层的图形信息相互传递

2) 支持将HFSS导入Cadence的Shape转换为独立的器件

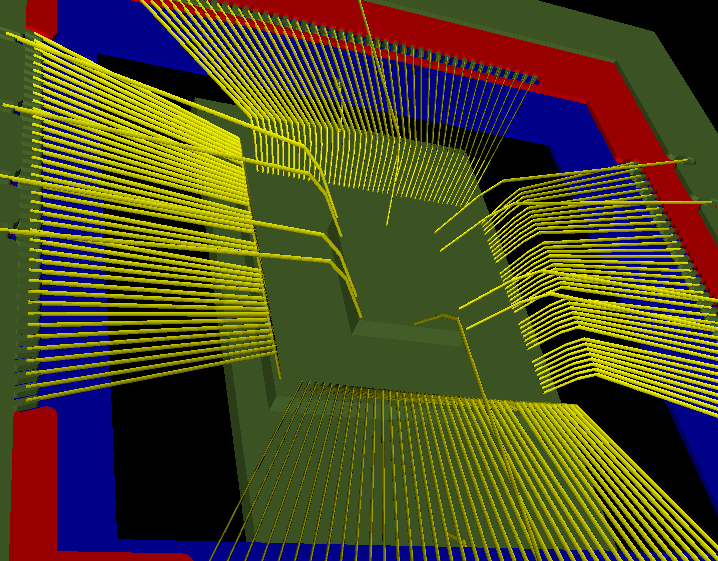

5. 支持3D封装寄生参数提取

传统PCB工具所无法进行的三维验证,Cadence-SiP拥有完善的三维寄生参数提取功能。全波领域的寄生参数提取和系统验证保证了设计的可制造性与可验证性,可以有效缩短设计后期的返工并减少后期的测试困难。

特色

1) Cadence-SiP整合并发展了针对SiP封装的3D视图以及规则检查

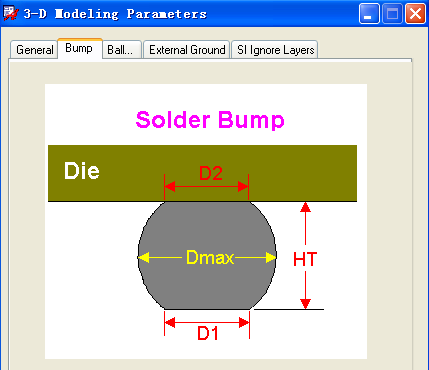

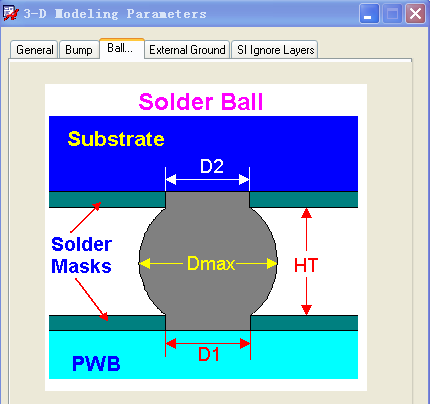

2) 金线、过孔、凸块、焊球等的3D属性帮助分析师成功建模

3) Cadence-SiP集成了针对微带线和带状线的传输线模型的分析工具以及高级过孔分析建模工具。

|