|

随着设计密度、复杂性和应用频率的提高,大量的信号完整性问题由此产生,使得传统的仿真迭代越来越耗时、繁杂,设计成本也会大幅增加。OrCAD Signal Explorer能够帮助设计者在设计进程中解决信号完整性问题,包括从开始的PCB布局到最后的PCB 布线整个进程。

OrCAD PCB SI与OrCAD Capture/PSpice Simulation/OrCAD PCB Designer等PCB设计环境实现无缝链接,可以在电路设计任意阶段提取信号拓扑结构执行SI仿真分析,避免了可能出现的转换问题。在OrCAD集成设计仿真环境中,设计的任意阶段――电路设计、Constraint约束规则设置,PCB布局布线阶段,甚至在电路板还没有网表和数据存在的原理设计阶段,设计师都可以对电路板进行高速信号拓扑结构的搭建或提取,并实时进行完整性分析,以随时知道PCB布局布线。

优点:

❁支持设计各个阶段的布线前和板级信号完整性分析,并确保与规则约束一致

❁允许互连拓扑结构的提取、分析与设计,可以有效提高电路可靠性和电路性能,降低原型产品的返工次数,降低生产成

❁能够直接提取OrCAD PCB Designer/Constraint Manager的电路拓扑结构,不需要设计数据的转换,就可以直接进行电路仿真,避免转换错误

❁提供一个简单方便的模型编辑环境,能够创建、修改和验证各种元件模型,用以快速提高模型或仿真的性能。

功能特性:

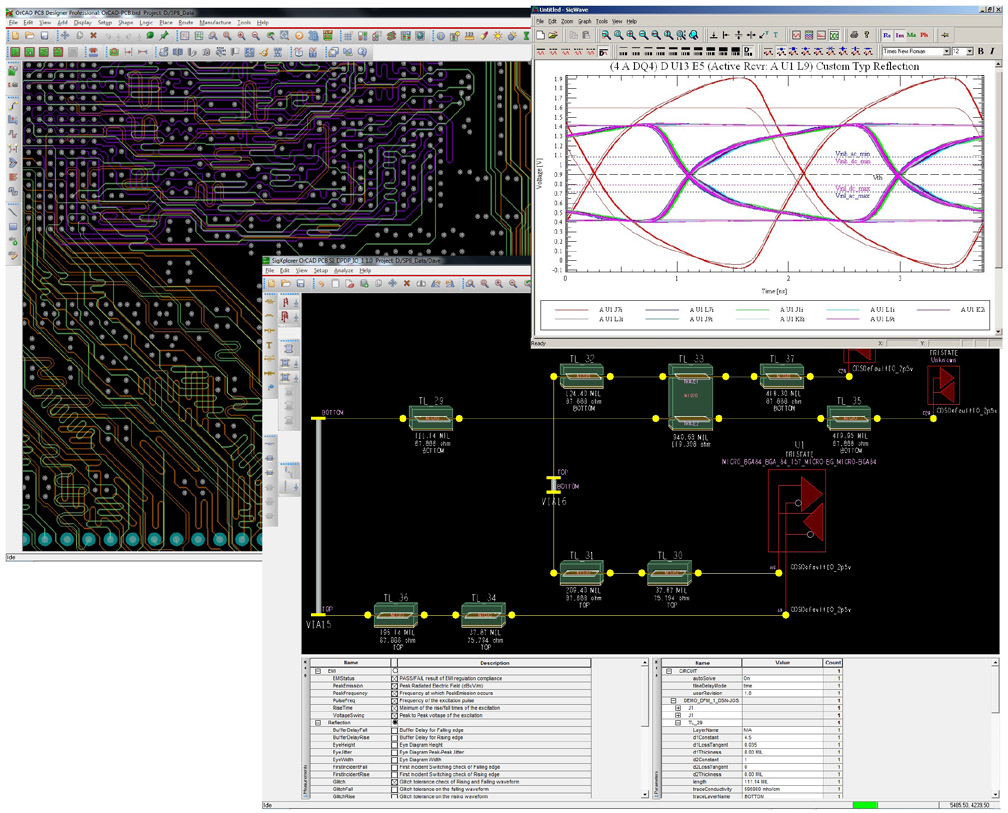

SigXplorer分析界面

OrCAD Signal Explorer 提供了一个电气图形界面口,用以观察电路的物理连接;一个分析空间,用以分析电路的临界高频信号。

在原理图创建前,用户可以通过SigXplorer模块对某一个网络的拓扑结构进行设计和分析。SigXplorer提供了各种带状线、微带线的有损模型与无损模型,用以进行电路的探索与设计指导。由于SigXplorer与OrCAD PCB Designer/Capture工具无缝集成化设计,用户可以在布线前或布线阶段将所要分析的网络直接提取到SigXplorer,然后用户可以使用基于SPICE的仿真工具对该网络进行快速分析。

SigWave波形窗口

SigWave模块可以将仿真结果以多种形式显示。示波器模式输出,允许显示个别波形,并提供相应标志便于屏幕测量;逻辑分析模式输出,总是伴随另外一个波形,因此电路的逻辑行为和总线报表更容易观察;频谱分析模式输出,用一种快速傅里叶变换技术显示信号的频域特性;视图模式输出,对于长模拟序列的模型观察是很有好处的。

SigWave同样允许直接输入其他波形数据进行分析,包括各种标准测试设备格式数据和信号完整性分析工具输出数据。

Model Integrity板级仿真模型编辑环境

Model Integrity模块为OrCAD Signal Explorer提供了一个模型编辑环境,可用来快速简单的创建、编辑和检查元件模型。这个模块包括一个模型浏览工具、IBIS模型的语法检查程序和DML模型的语法检查程序。OrCAD

Signal Explorer接受各种数字化建模格式的硬件模型,包括标准的IBIS建模语言――这就意味着大多数半导体厂家的产品模型都可以使用。此外,OrCAD Signal Explorer提供了下一代用于复杂设备的建模语言DML,这种可扩展的宏建模语言提升了IBIS模型,可以为先进的I/O功能模块快速准确的提供相应模型。

高精度仿真引擎

Tlsim仿真引擎结合了具有传统优势的基于SPICE的结构建模工具和高效的电路行为分析工具,它包括一个IBIS类型的行为驱动元件,这个驱动元件的I/O行为模型是在行为建模技术提供的V-I、V-T数据基础上建立的。结合了行为建模和结构建模技术,Tlsim使得复杂设备行为的建模技术更加精确和高效。这个仿真引擎中包含一个有损的、基于频率特性的传输线模型,它可以准确的预测PCB走线在几GHz频率内的行为特性。完整的电气领域的解决方案,可以确定布线层的电气特性,并为PCB过孔创建电气模型。

|