|

OrCad Sigrity ERC(Electrical Rules Check)提供电气规则检查的技术,让PCB设计人员在没有仿真模型或大量的信号完整性专业知识,也可轻松、快速地识别信号的质量问题及其因素。

Sigrity ERC突破简单的几何设计规则检查(DRC),识别信号的质量问题,一般仅通过先进的SI/PI工具发现。

Sigrity ERC完全整合PCB Editor,使PCB设计者直观的在PCB界面中发现问题,做出转换,并验证ERC已纠正。

概述

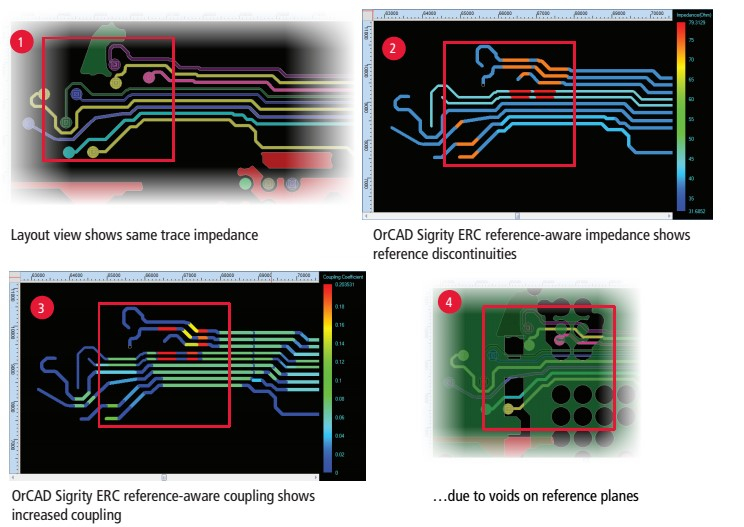

Sigrity ERC使PCB设计师可以检查和发现信号质量的问题,而以往这些问题需要通过复杂的仿真工具和SI工程师来验证。使用ERC/SRC(基于仿真的规则检查),在PCB布局布线设计时就能够发现信号质量问题 以便先行排除潜在问题,从而节约整体设计时间,减轻SI人员的负担,大大提高效率。

在确保信号质量有效性方面,ERC/SRC要胜于DRC.是对DRC的补充。Sigrity ERC提供易用的界面简便的设置和PCB布局设计交互式样。Sigrity

ERC提供可操作的结果,识别和快速解决信号质量问题。

优势

❁ 无需模块要齐--PCB工程师易于使用

❁ 检测阻抗不连续的路由PCB信号

❁ 检测布线引起的PCB信号之间的耦合

❁ 结合PCB设计,便于调整信号-阳离子的问题

功能

Sigrity ERC是一个易于使用的参考感知走线阻抗,先进的PCB布局的信号质量检测耦合和参考检查工具。可提供三个选项

• 检查所有网络属性

• 检查选中的网络属性

• 通过Group来检查

Sigrity ERC产生阻抗和耦合叠加,布局走线用颜色标识阻抗和耦合系数值。覆盖图清楚地表明由于跨参考平面而增加阻抗和耦合,这在板级上单靠目测几乎不可能识别。

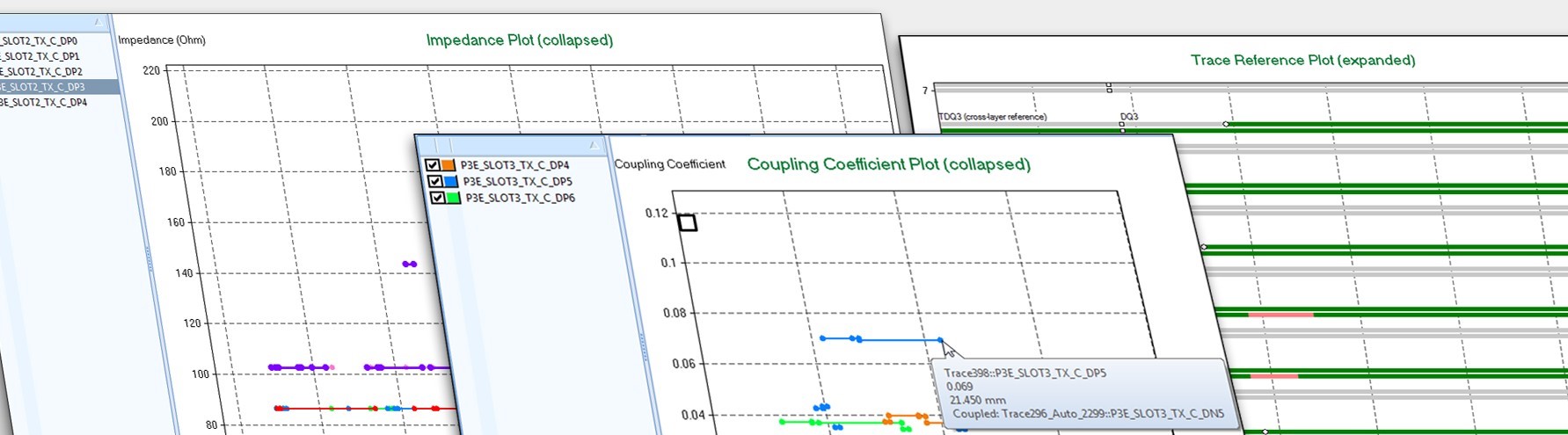

概括性结果一览表

Sigrity ERC 将结果生成用户易懂的图形表格形式

❁ 走线分段分析结果

–相对位置阻抗

–相对位置耦合

–上下层参考

–共面参考

❁ 网络级分析结果s

–阻抗总况

–耦合总况

–长度与延迟

–R, L, and C

–阻抗参考不连续的数量

–没有参考平面的线段数

–过孔数量

❁ 板级分析结果

–走线区域

–布局区域

–布线引起的效果

高端信号检查工具

Sigrity ERC同时包含SRC环境参数。网表级pcb layout 检查工具是以时域仿真为基础和考量

• 失真

• 延迟

• 终端阻抗不连续导致的反射

• 信号线耦合

• 过孔耦合

Sigrity SRCSRC会将加载的几何结构做讯号批次检查SI metrics Check,并列出讯号的被影响程度如:

• Tx/Rx相关:发射端和接收端的讯号质量。

• NEXT/FEXT相关:近端和远程被其他讯号干扰的程度。

其结果以HTML报表来列出讯号Tx/Rx/NEXT/FEXT的影响程度,或是以Excel列出前十大干扰源之讯号名称。

|