|

���ȣ�������Ҫ�����迹�Ż��Ķ�����Դƽ�棻Ȼ��������Ҫ����ƽ���迹��Ƶ�����ԣ���ֱ����Դϵͳ�л���Ӹߴ��Ʋ����Ʋ���ƽ���迹��Ӱ�죨�迹ԽС�Ʋ���Խ�ܱ������գ����ٴΣ�����Ҫ����Sigrity��ƽ���迹��Ƶ���������������1V���ҽ�����ѹԴ�Ե�Դ����˿ڽ���ɨƵ�������õ�����Ƶ����ƽ���迹ֵ������ȷ������Դʹ�ö˿��迹ֵ�����������Ҫ����Sigrity����ƽ���迹��Ŀ�꣬����ͨ��������ͬƵ�ʵļ�������ƽ��˿ں�ı����迹���ԣ�������������Դ��ͬƵ�ʵĸ�Ƶ�Ʋ���Ӧ��ƽ���迹��

ƽ���迹��������ʵ��Ӧ�ľ���ֱ����Դ�в��ӵĸ�Ƶ�Ʋ��ĶԵ��迹���ԡ�����ƽ���Ƶ�迹С����Ƶ�Ʋ���GND����Ժã��������Ա�������գ�����EMI���⣻��Ƶ�迹г��㣬����Ƶ�Ʋ���Ӧ���迹���Ӧ���Ǹ��Ʋ���GND����Բ����Ʋ����������ĵ�Դ������ϵ������У�������������ʹ��Σ���ԣ�ͬʱ��������EMI���⡣

Sigrityƽ���迹г��������Ż������Ż���Դ-�ص�����ԣ����ֱ����Դ���������Ӷ�ȷ�������ɿ��ԣ�������EMI���⡣

1. PowerSI��ȡS/Z����ģ��

PowerSI�����������Զ�������ȡ����PCB�ϵ�Դƽ��������źŵ�Ƶ�����ԣ���ƽ�����źŵı���Ƶ�����ԡ��Դ�Ϊ�������������Խ��и����źŵ�S����ģ�ͣ�������Sigrity SPEED2000/SystemSI�н���ʱ�������ͨ��������Ҷ�任�㷨�����Ƶ��תʱ�������źŵķ��䡢���š�ʱ����������ܣ�Ҳ����ͨ��OptimizePI��ƽ������Զ��Ż��������������ǿ���ȷ���ϼѵ�ȥ������Ż���������Ч������Ч�ʲ����Ƴɱ���

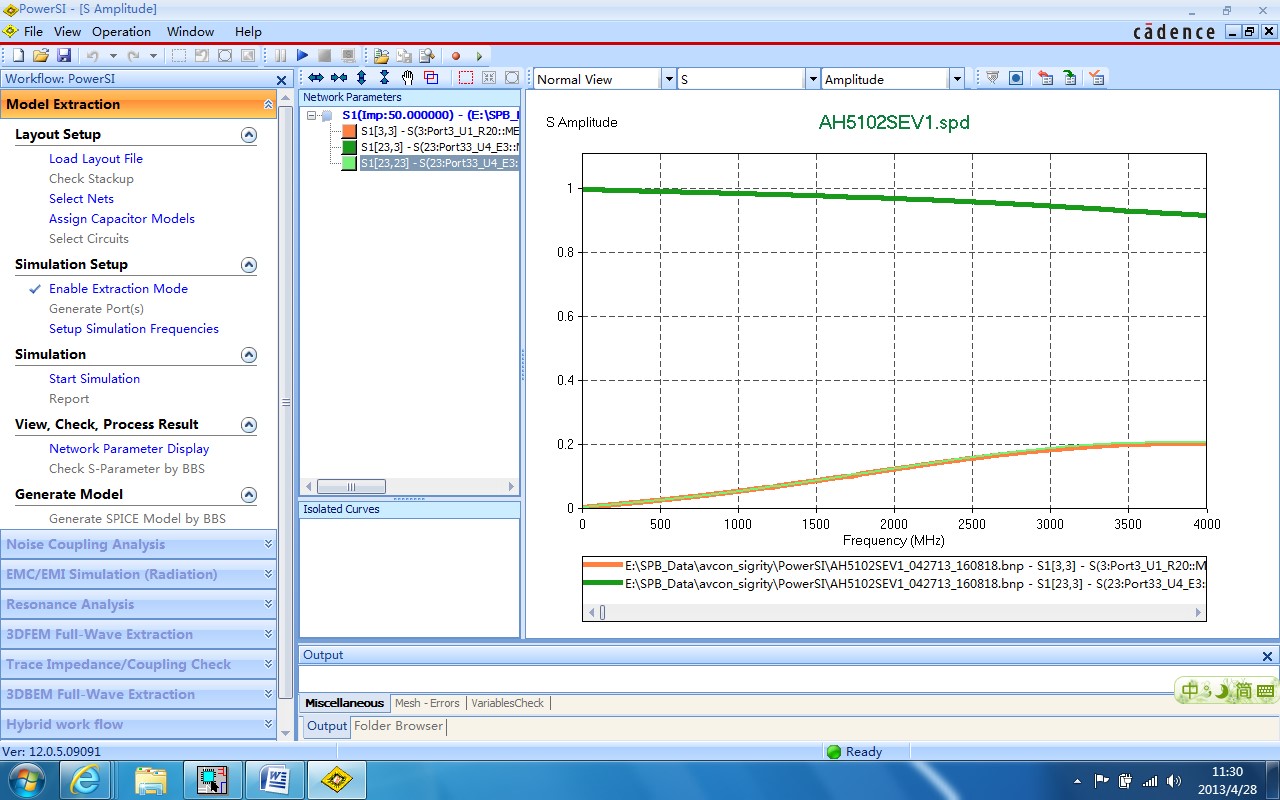

ͼ1�������ź�S����ģ�����ߣ��������š����𡢲�������

S����˵����

�������ߣ��źŻ�·���ź�-GND�����������ı�����ֱ������ź���ȫ���䣬�������S12=1���ź�Ƶ����ߣ������ź��л��𣨷��䣩���������ߴ�ֱ��1��������ģ�����Ƶ����߶��½���

�������ߣ��źŻ�·���䣨�ź�-GND��������ֱ������ź�û�з��䣬����S11=0���ź�Ƶ����ߣ������źŷ������������ߴ�ֱ����0����Ƶ����߶�������

�������ߣ������ź�֮��Ĵ��Ų���S13������1��2Ϊ�ź�DQ0�����˿ڣ�3��4Ϊ�ź�DQ1�����˿ڣ����������߲���S13����Ƶ����߶���0������ֱ�����ţ���

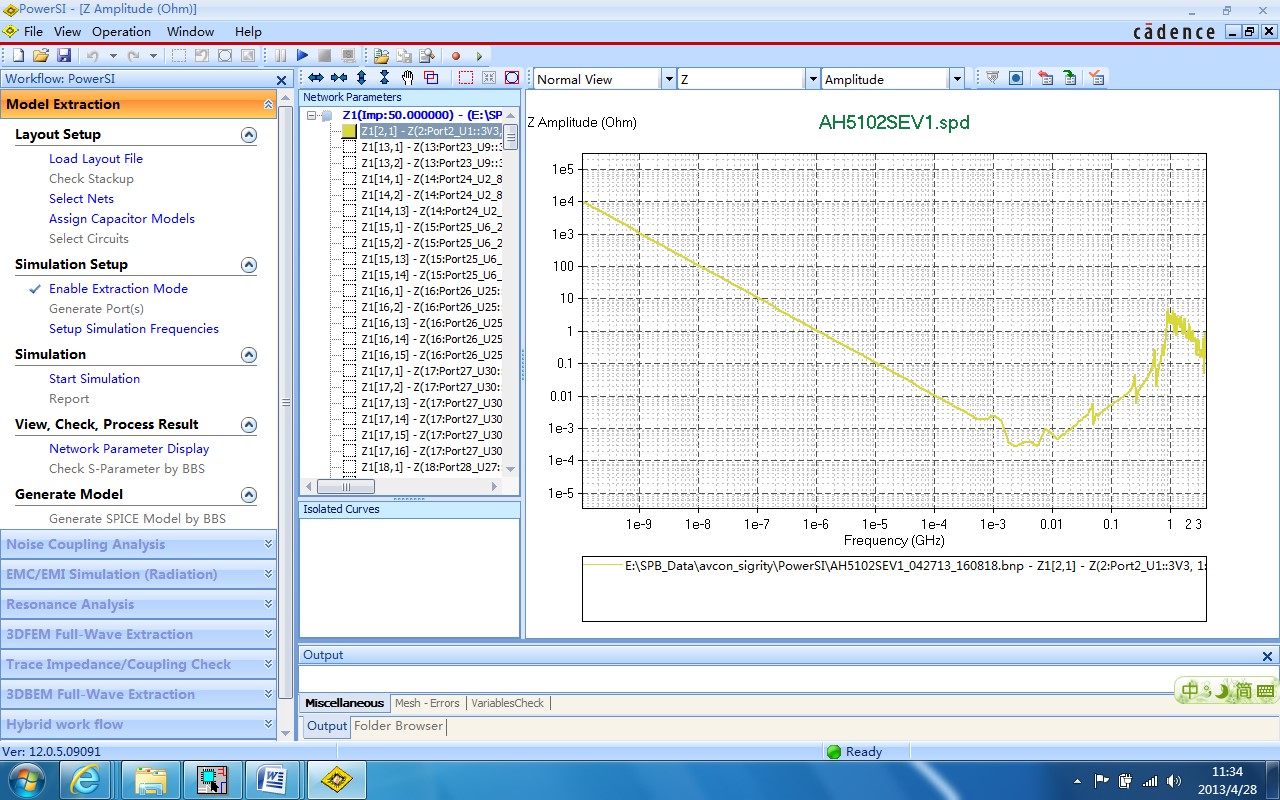

ͼ2��ֱ����Դ�ϵĸߴ�г����ƽ���迹���Ե�Ӱ��

Z����˵����

���ȣ�ֱ����Դ��������������ֱ�������Dz����źܶ�ߴ�г��������Դ�Ʋ�����ͬƵ�ʵĵ�Դ�Ʋ��Ե�Դƽ�汾������ЩӰ���أ�����ͨ��Z����ģ�����������⡣

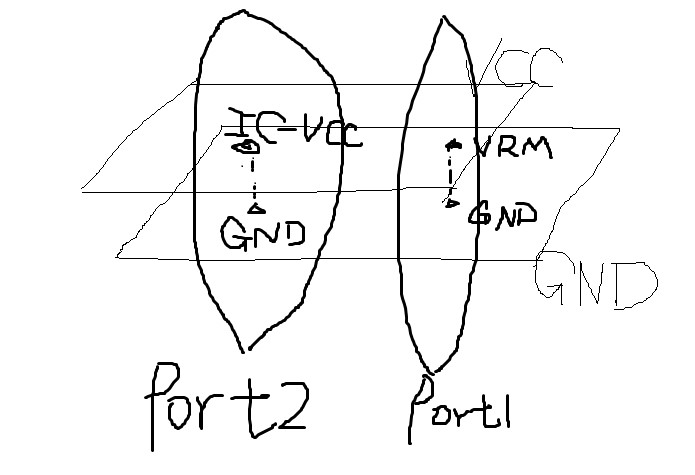

Z������û�в��������ĸ��Z���������Ա���ƽ��-GNDƵ��������ԣ������ǹ���״̬�����������ǵ�Դ��VRMֱ����Դ�����Ʋ�������˿ڣ�Port1=VRM-GND������������Դʹ�ö˿ڣ���ԴPin����Port2=IC-VCC-GND���Ļ�·�迹��2�˿����磬����ͼ��ʾ����

Z���������У���Դ��Ƶ�迹ԽСԽ�ã����ߴ��Ʋ���GNDƽ�������Խ�ã��ߴ��Ʋ���GND���յ�����Խ�࣬��IC-VCCʹ�õ�ֱ����Դ��Խ�ɾ����ܹ���Чȷ��������Դ�����ԣ�����EMI��

��Դƽ��ij���˿ڣ�Generate

Port�õ��ģ������迹��������Ƶ���Ʋ��迹֮�ͣ�ZDC+Z1MHz+Z10MHz+���������⽫��OptimizePI��ƽ���迹���Զ��Ż��Ļ�����

ͼ3����Դƽ���迹�����˿ڶ���

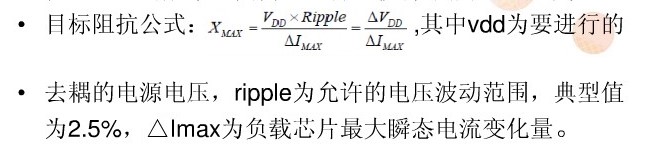

2. Ŀ���迹Target Impedance

����PowerSI��ȡ�ĵ�Դƽ���Z����ģ�����ߣ������Ѿ�������ʶ��Ȼ����Щƽ���迹Ƶ�������Ƿ�������ָ�꣬�Ƿ���ȷ����������ж��أ���������Ŀ���迹���ж������ݡ�

Ŀ���迹����������������Χ�������ĵ�Դϵͳ��˲̬�迹���Կ��ٱ仯�ĵ��������ֳ�����˲̬�迹�����Դ�ߴ��Ʋ��ĶԵ���������йء�������Ŀ���迹���Ƶ�Ʋ��йأ�PowerSI���������������Ƶ���������Ƶ�Σ�Ҫȷ�������ϵ�Դ����Ƶ���迹���ڴ�Ŀ���迹������ȷ��ֱ����Դ�Ĵ����ԣ���Ч����EMI������������Դ���������⡣

ͼ4��������Դ����Ŀ���迹�ļ���

Ŀ���迹Ϊƽ���迹Z����ģ�����ߵIJο�ֵ������Ƶ�Ƶ���ڵ�Դ�����VRM/������ԴPin��IC-VCC���迹����Ŀ���迹ʱ��VRM��Դ���VRM-GND/������Դʹ�ö˿�IC-VCC-GND����Զ��ȽϺã����Ƶ�εĸߴ��Ʋ����ɱ�GND���գ���������ȫ�ɿ���ʹ�øõ�Դ����ƽ���迹��ijƵ�εĵ�Դ�迹��VRM/IC-VCC������Ŀ���迹ʱ��VRM��IC-VCC��GND����Բ���Դ�������ܱ����գ���Щ�ߴ��Ʋ�����ϵ���Դʹ�ö�IC-VCC��������ʹ�õĵ�Դ���ɾ����ᵼ�µ�Դ��������EMI�����⡣

�ɴ˿ɼ���������Ҫ����Ŀ���迹���Ե�Դ�˿ڣ�VRM/IC-VCC���迹�����Ż�����ʹ��ﵽ������Դ�˿�Ŀ���迹��Χ���ɴˣ����Ǿ���Ҫȥ�����Ӧ��ȥ��Decap/��·Bypass���ݣ��Ա�����ƹ���Ƶ�ε�PI/EMI���⡣

���ۣ�Ϊ��Ҫ��עг��㣿

����г����ƽ���迹�ᷢ��ͻ�䣬г�����迹���͵�Ŀ���迹���£����ܹ�ȷ����ϵƵ����ƽ���迹��Ŀ���迹��Χ�ڡ�

����г���д���г��Ͳ���г�������迹�ķ�ֵ��ֵ������Ҫ�����ǽ��ͷ�ֵ�迹��

3. ����Sigrity OPI��ƽ���迹�Ż�����

OptimizePI�����Զ���ѡ��ͷ���ȥ�������ȷ����Ʒ����Ե͵ijɱ������Դ����ϵͳ��PDS��������Ŀ�ꡣ���Ժܴ��ȵĽ�ʡ��ƿռ䲢�ҵ�һϵ�еĽ��ű�ѡ���ݣ��Ӷ�ָ�����ǽ��о����PDS�Ż���

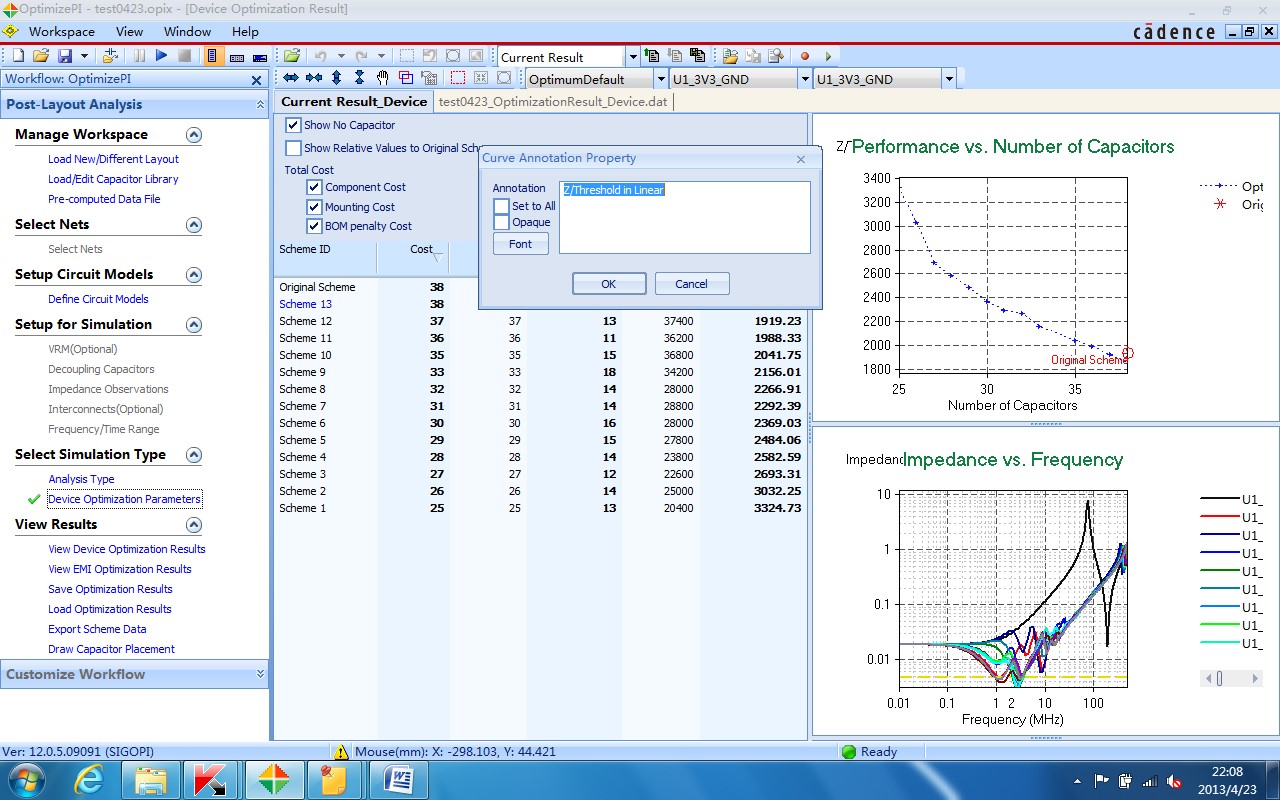

3.1 OPI �CImpedance Linear�����㷨�Ż�

�����迹�Ż������Ż��㷨�Ե�Դƽ���Port�˿ڴ��迹�������Ե��Ӽ��㼰�Դ����Ի��������Ż�������

�������£�

��Դƽ����1MHz����Ӱ���£��迹Ϊ0.1ohm��

��Դƽ����100MHz����Ӱ���£��迹Ϊ10ohm��

�������Դƽ����1MHZ��100MHz�źţ�������Ӱ�������迹Ϊ10.1ohm�������˿ڸ���Ƶ���迹������ӣ�

�������Ż��㷨�����ǽ��������迹��ͨ��ȥ�����ѹ�ͣ����Ż������ȼ��ִ��迹���������ĸ��迹���㷨�������Ż��ĸ�Ƶ�㣬Ȼ���ٿ���С�迹��г��Ƶ�㡣

�����У��Ż���Ȩ��0.1ռ10%��10ռ90%�����㷨���Ƚ�100MHz���迹ѹ�ͣ�����8ohm����������Ż�1MHz��0.1ohm�迹������0.08����

�����ȼ����������õ�Ŀ���迹����ϢϢ��ء�

������ʦ�бȽϹ�ע��Ƶ�㣬������У��ҶԸ�Ƶ100MHz���迹�������ǣ�������أ�����Ҫ�ص��ע1MHz��г���迹�Ż��Ļ�����ʱ�����Ǿͱ���ʹ�ö����Ż�������

ͼ5��OPIƽ���迹�����Ż���ʽ

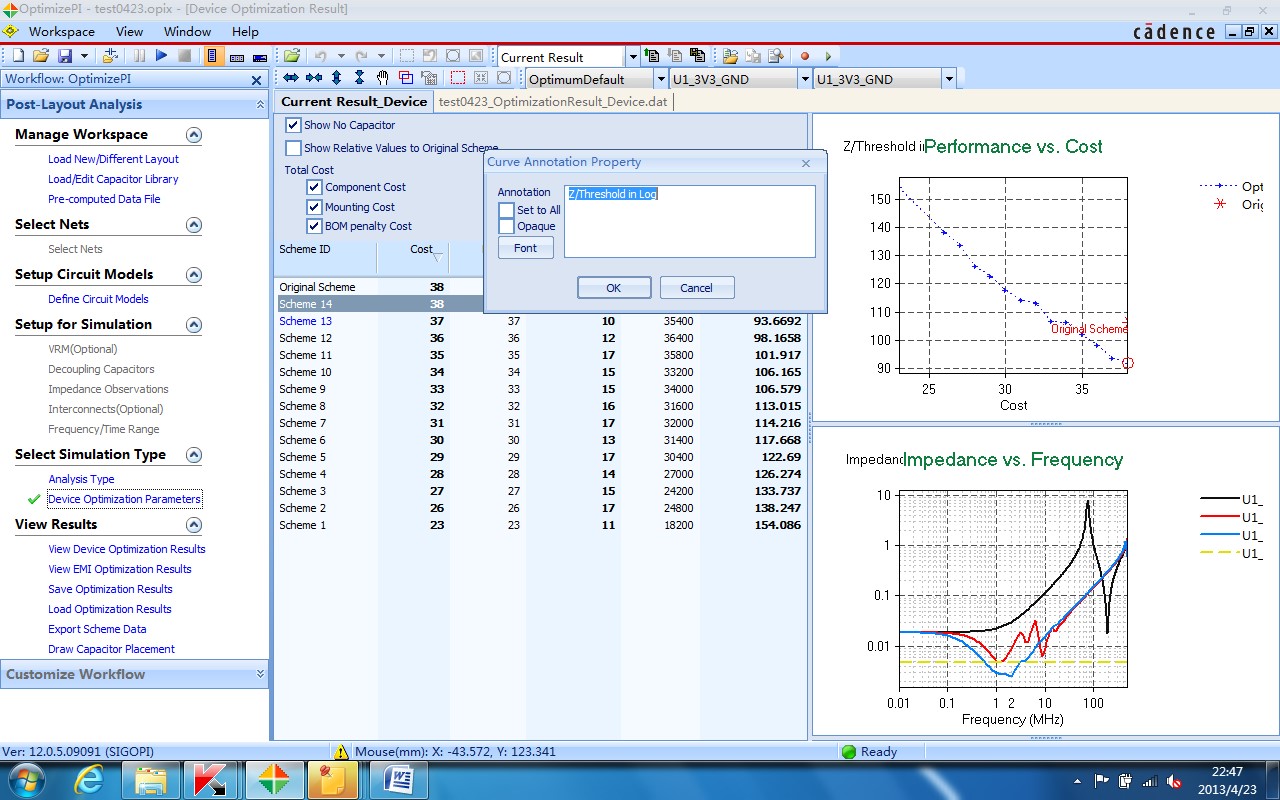

3.2 OPI-Impedance Log�����㷨�Ż�

�����迹�Ż������Ż��㷨����Դƽ��˿ڵ��迹��ȡ������Ȼ�����迹����Ϊ��������˿ڵĶ������迹�����Զ�����ʽ���Ż��������Ż������ȼ�����

�������£�

��Դƽ����1MHz����Ӱ���£��迹Ϊ0.1ohm��

��Դƽ����100MHz����Ӱ���£��迹Ϊ10ohm��

�������Դƽ����1MHZ��100MHz�źţ�������Ӱ���¶������迹Ϊabs(log0.1)+abs(log10)=1+1=2���������˿��迹�Ķ�����ӣ�

�������Ż��㷨����ͨ�����Ӳ�ͬ��ȥ����ݷ������Լ�С��Դƽ��Ķ˿ڵĶ������迹���Ҵ�ʱ�Ż������ȼ����Ƶ����Ƶһ�£�����ֵ������ȣ�����������ʽ�Ż�ʱ���㷨��ͬʱ��С1MHz��0.1ohm��100MHz��10ohm�迹��

�����ĵ��ݷ����У������Ż����㷨�������ص��Ż��迹�ߵ�Ƶ�㣬��ɺ�Ż��ڴ˻������Ż���Ƶ�㣻�����Ż����㷨��ͬʱ�Ż���Ƶ���Ƶ���迹������

ͼ6��OPIƽ���迹�����Ż���ʽ

�ܽ���ص�������Դ�ĸ�Ƶ�Ʋ��������������㷨�Ż��ʺϣ����ߵ�Ƶ�����ص�����������������㷨�Ż��������Ӻ��ʡ�

|