|

PowerSI新功能

自动设置Special Void

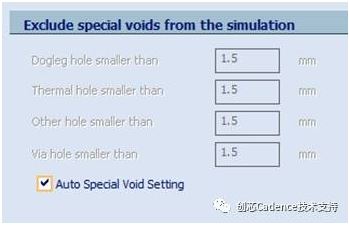

• Special voids作为负片铜皮的避让区域,在仿真中这些区域要被排除

• 为了加快仿真速度、提高网络过孔的仿真精度,典型方法是忽略小尺寸Hole

• special void尺寸确定标准非常困难,如何避免转换数据不完整?

- 全新的Special Void自动设置功能,完整、自动地创建Void转换设置,避免设置经验不足带来的转换问题,且有效提供了仿真精度

- 新增Special Void options设置

- 在Stackup叠层设置窗口,可以分别针对每一层进行SpecialVoid参数设置

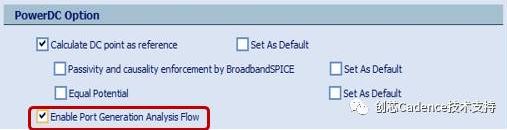

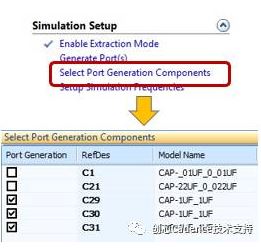

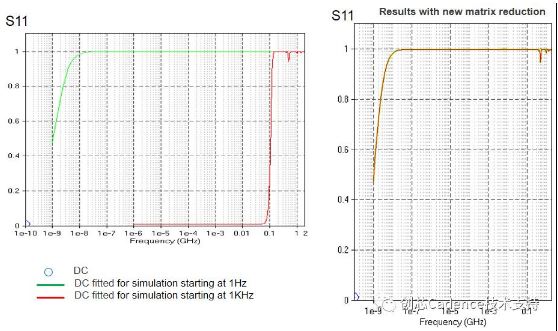

全新Port创建流程提高Low-Frequency精度

• 为了提高电容配置规模大的PCB设计中DC-AC仿真精度,PowerSI提供全新的端口设置技术

• 技术暂时替换在用户指定 N个器件端口的去耦模式,允许 PowerSI技术提取“空载"的模型,并专注于设计本身的寄生效应模型

• 仿真可与额外的N 端口一起运行

– 一旦结果被提取,PowerSI技术通过终止其组件的电气模型与这些N 端口时,将自动执行端口减少

• 最初的端口数给出了网络参数数据

改进的低频率准确度的新端口生成工作流

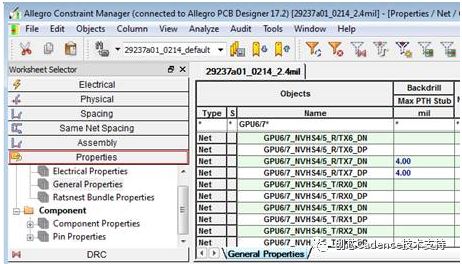

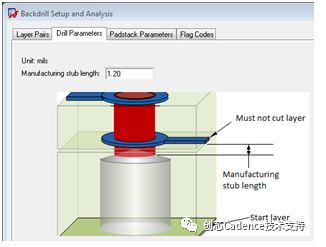

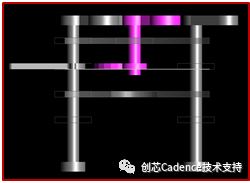

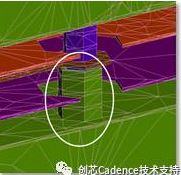

从Allegro环境直接提取背钻结构

• 目前Allegro设计中背钻孔可以直接转换至PowerSI仿真流程

–支持PCB中间介质层出发的Via Stub

–3D viewer可以清楚了解Via Stub结构

3DEM新功能

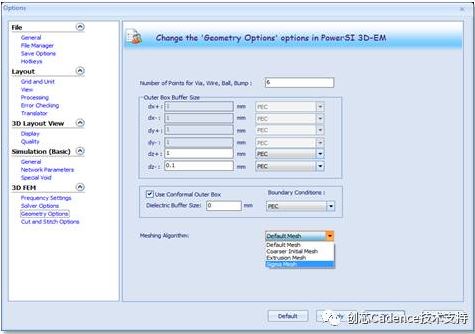

Sigma Mesh in Meshing Algorithm

• Sigma Mesh是全新的Mesh算法

• 对于某些项目,Sigma Mesh可以创建更好的初始网格,有效减少网格数量

• 如果Sigma Mesh无法创建初始网格,DefaultMeshing算法将重新创建初始化网格

• 对于某些项目,Sigma Mesh能够创建更好的网格,有效减少网格数量,并减小电脑内存使用量

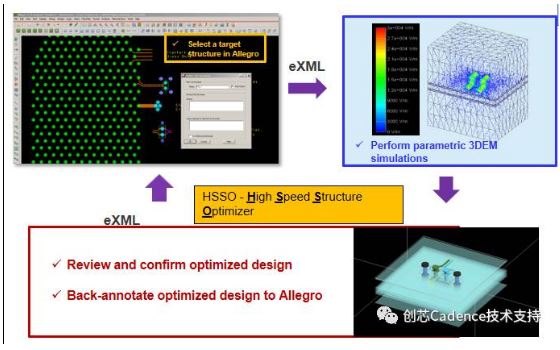

3DEM Full-Wave HSSO Enablement

• Sigrity 2017新增过孔阵列优化流程

环境变量设置“WORKFLOW_3DEM_HSSO = 1”

–Open3DEM

–SelectFile->New->workspace,choose 3DEM High-Speed Structure Optimization

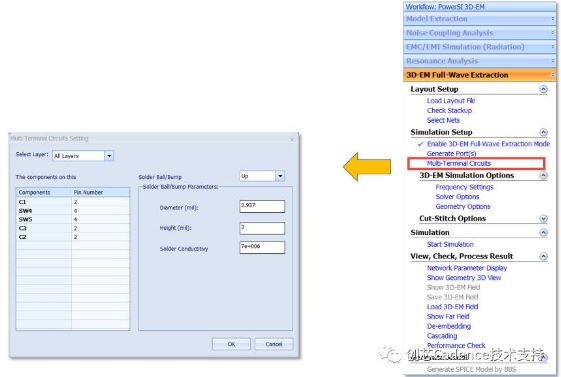

Multi-Terminal SPICE Model Circuit Support

• 无源器件的全新仿真设置

– 支持RCLK SIPICE模型

– 支持嵌入式器件

– 可以根据Layer设置,也可以全体批量设置

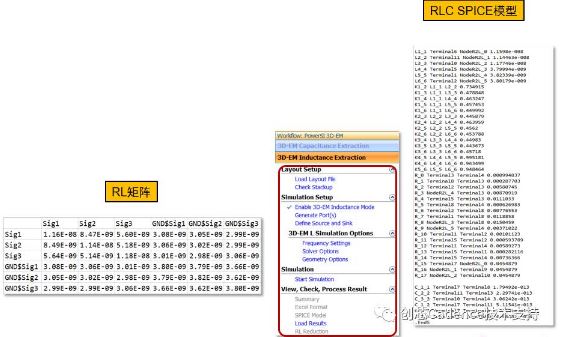

Partial Inductance Extraction by QS Solver

• 3DEM InductanceExtraction仿真流程可以根据所选S/P/G网络提取网络的局部等效电感(QS Solver)

– 以Text/Table格式,输出网络局部电感矩阵

– 输出RL SPICE模型

– TCL命令可以将RL SPICE模型合成为RLC SPICE模型

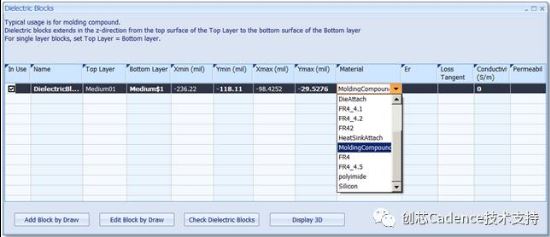

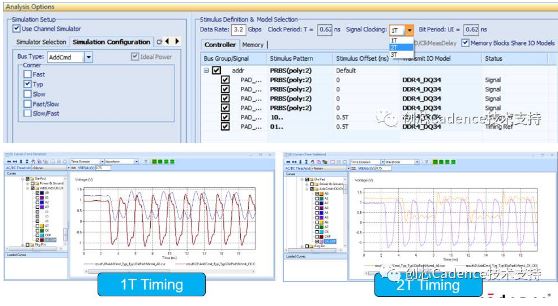

Use Material Library in Dielectric Blocks

• Dielectric Blocks表格新增一列,用以从材料下拉清单中选择

– 从材料库里面选择材料名称,原来的Er/LossTangent/Permeability材料属性列都被取消了

SystemSI新功能

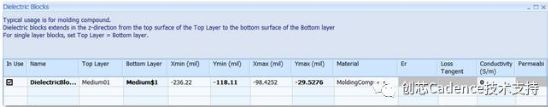

S参数仿真选项

• 强制为S参数提高Passsivity性能,并移除其中DC结果,提高仿真可行性

• 可用于串行通道AC耦合电容分析

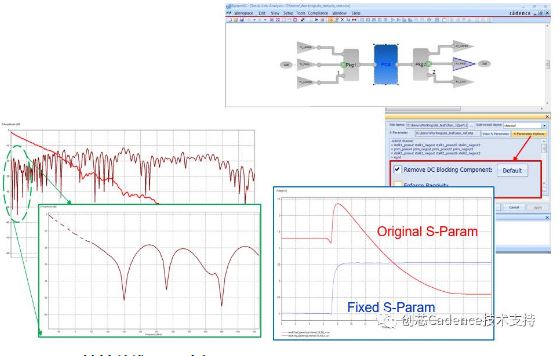

2T/3T DDR 地址总线CLK时序

• 地址总线2T/3T时序仿真,仿真设置可以直接在Analysis Option中完成

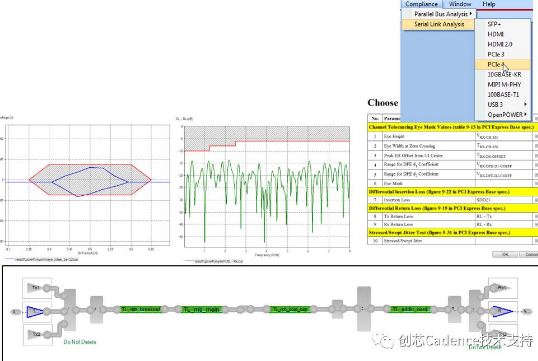

PCIe Gen 4 Compliance Kit

• Data速率16Gbps

• 基于规则的自动检查

• FFE/CTLE/DFE包含spec-level的AMI模型

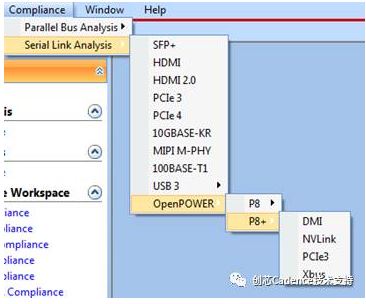

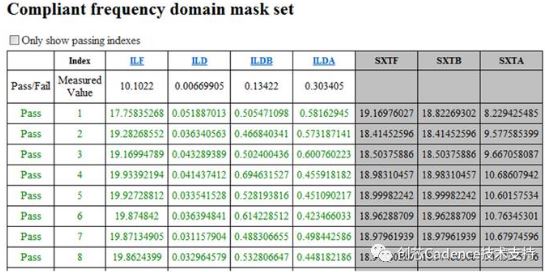

OpenPOWER P8+ Compliance Kit

• 仿真模板与自动检查功能,可以支持DMI,NVLink, PCIe3, and Xbus等接口

• 根据广泛的规则检查频域结果的合理性(IBM开发)

Sigrity 2017是Cadence系统设计使能的重要技术,从芯片、电路板、到全系统,助企业打造创新的高质量电子产品。

如需了解有关Sigrity 2017系列产品的更多内容 。可以通过e-news@u-c.com.cn来索取,或致电技术服务热线4007-188-616与我们联系。

|