|

电子设计自动化领域领先的供应商 Cadence,与诸位分享Cadence Allegro、Sigrity等产品新的科技成果和进展,并向电子设计工程师展示Cadence独有的PCB和封装设计解决方案。下面给您带来一篇发布于SemiWiki.com的文章“PowerTree: PCB电源分配网络的数据存储和仿真平台”。

在复杂SOC片上系统管理电源网络十分复杂,这促进了电源格式文件描述的发展,从而为功能分析和电气分析存储数据(如CPF、UPF等)。然而,对于复杂的印刷电路板,情况是怎样的呢?电源网络的信息如何得到有效体现(一块或多块板)、并存储下来用作后续的分析?电气分析如何有效融入PCB设计、减少PCB优化的时间?PCB电源格式信息如何能被自动提取、并传递到仿真?

具体来说,对于复杂的电源分配网络(PDN),加速电源完整性分析过程中的主要问题有:

Cisco近期分享了一个关于电源网络拓扑的实例,来自于他们的新产品――包括约20组电源,约250个元件,以及近500个电源网络(包括滤波器件周围的网络)。具体来说,系统级电路板的设计包括使用多样的元器件类型,来满足I*R (DC直流)电源压降和电源阻抗特性需求(基于频域的交流AC阻抗需要考虑较优去耦电容的大小和位置)。

我最近有机会跟Brad Griffin进行了交谈,他是Cadence Custom IC & PCB Group的产品总监。Brad描述了Cadence是如何帮助客户,实现将PI分析引入设计流程中。“在Cisco等客户的帮助下,我们开发了新的功能用于Sigrity电源完整性和OptimizePI。PowerTree的存储是一个独特的方法,可用于生成并图形化地显示复杂电路板设计信息及相关元器件模型及约束。”

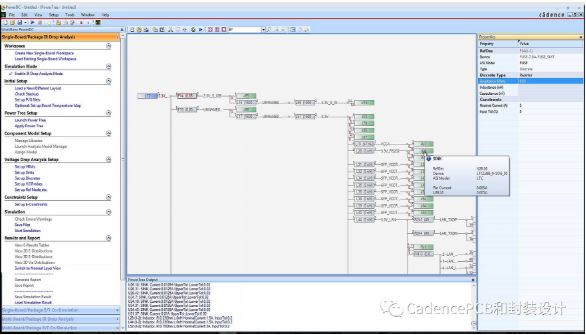

PowerTree的配置很直观――如下为“建立PowerTree”对话框的截图。

如下为一个复杂PDN的PowerTree应用的截图。

元器件清单和连接网表都来自Cadence Allegro。一个简单的PowerTree视图就可以包括大量原理图页面的电源网络信息。元器件模型提供了电气行为和验证检查约束。设计工程师可以在PowerTree中加入额外的设计约束和元器件模型数据。Brad强调:“通过PowerTree环境,在Sigrity PowerDC 中PCB设计工程师可以快速在原理图和PCB布局布线过程中生成和运行DC分析仿真,优化DC之后,将设计提供给电源完整性专家,进行去耦电容选择和放置,来优化频域电源阻抗。PI专家收到了更高质量的设计,可以使用Sigrity OptimizePI来展开工作。”

Brad和我都知道电源完整性专家是非常宝贵的资源,他们经常工作负担过重。PCB设计工程师可以使用SigrityPowerTree的特性,快速提取电源拓扑结构以及元器件数据,进行仿真来保证提供PCB的DC需求,这将大大提高PI分析工作效率。

|