|

随着集成化程度的提高,印制板设计中FPGA及其引脚数量越来越多,设计难度越来越大,Cadence FPGA System Planner设计平台正是为了应对如此愈发复杂的设计挑战。它从创建初始引脚配置着手,紧密结合原理图及PCB设计工具,确保复杂PCB布线顺畅。CadenceFSP系统设计平台提供了一套完整的、可扩展的FPGA-PCB协同式设计解决方案,用于板级FPGA设计,能够自动对引脚配置进行“芯片-规则-算法”的综合优化。

Allegro FPGASystem Planner集成了Design Entry CIS和Allegro PCB Editor模块,可以直接读取和创建Capture原理图和符号文件,也可以直接在创建PCB布局。Allegro FSP可以实现与Allegro布局的双向交互优化。

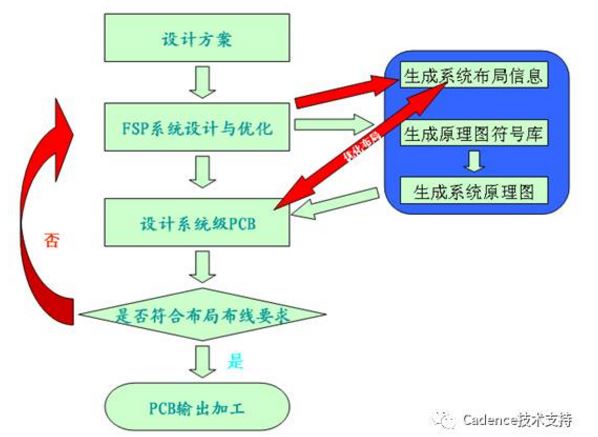

Allegro FSP 具体如何来实现FPGA-PCB的系统协同设计,可以从下面的流程阐述中了解到。

首先,从下面的图中可以看到FSP进行系统级设计开发的流程:

Allegro FSP设计流程完全与HDL、CIS两种Cadence原理图输入工具及AllegroPCB设计工具紧密集成,可以完成FPGA-PCB的协同设计。

接下来,将为FSP的协同设计流程及其库的创建作具体的阐述,Allegro FPGA System Planner设计流程详解:

1、新建FSP工程项目,并做好基本设置

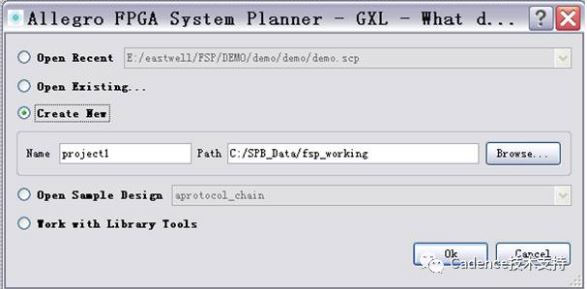

(1)执行CadenceRelease 17.2/FPGA System Planner,如下图:

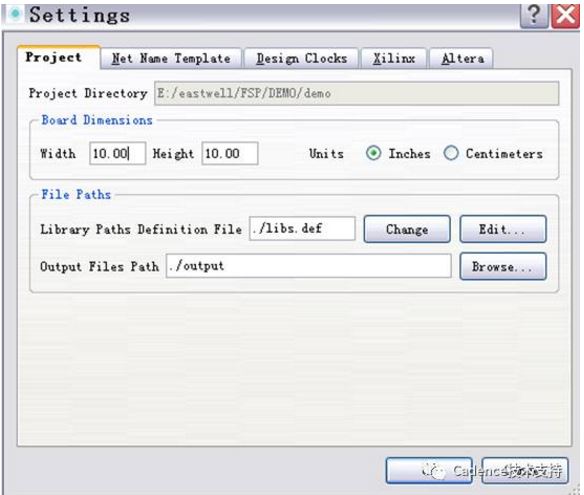

(2)点击OK进入设计基本设置栏,设置页面尺寸、调用库及输出路径等。

注意这里的页面尺寸,就是后期设计中的PCB尺寸。

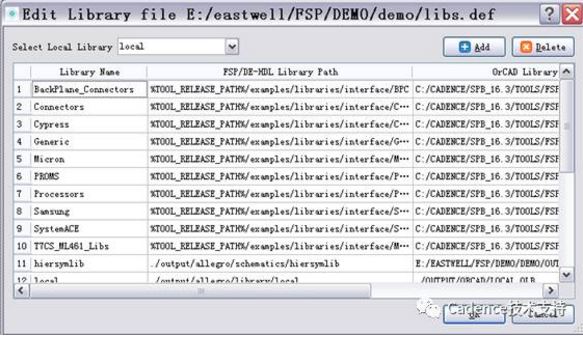

其中Board Dimensions设置页面尺寸,这个尺寸以后将被导入PCB作为PCB的outline;outputfile path栏设置设计输出路径;Library Path设置调用的库路径,点击Edit可以编辑设计库如下图。

需要添加新的器件库时,点击右上角的Add按钮,选择库路径即可。

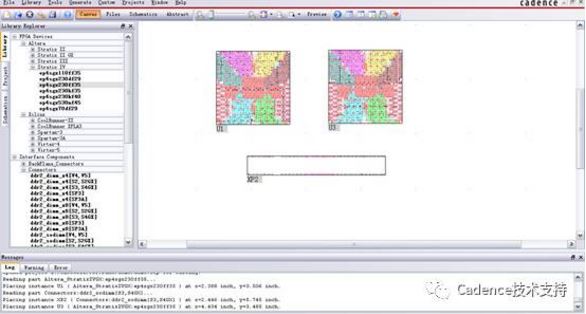

2、在设计页面中,添加所需FPGA和Interface,这里用于FPGA-PCB协同设计,暂时不添加外围元器件,外围元器件在生成的Capture或HDL原理图中添加(如下图)。

FSP中添加FPGA和Interface

3、元器件放置完成后,就需要在FSP中设置元件之间的连接关系,并且为网络连接赋予FPGA相应的连接区域,这个区域是用于后来连接关系优化走线的区域。

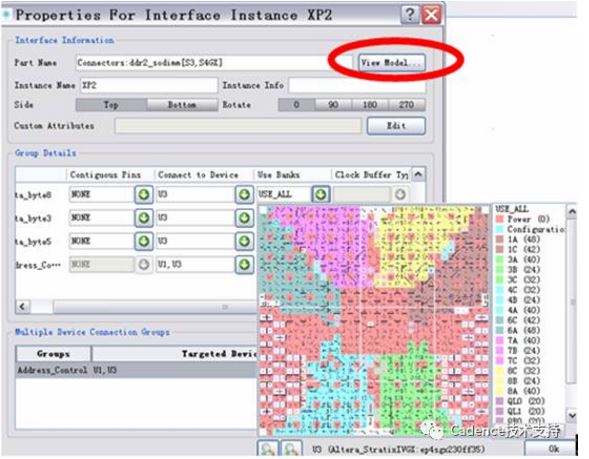

(1)实现FPGA与Interface的连接关系:右击Interface器件,选择Instance Properties命令,如下图所示,选择总线连接的FPGA及其连接区域。

选择器件连接关系及网络所在设计区域

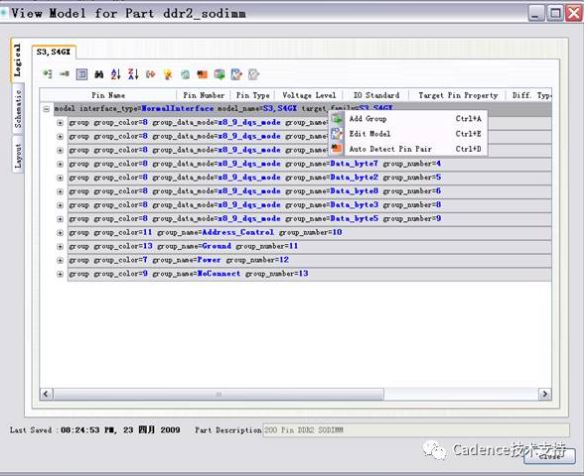

此时,点击View Model,得到下图所示的Model编辑对话框,其中:Logic选项卡中,可以编辑该器件的Group、Constraint等元件连接属性,更用来定义该Interface与哪些系列的FPGA相互连,是Model编辑中较为重要的一环;Schematic选项卡,用来编辑并实时观察器件原理图符号;Layout选项卡,用来观察和编辑器件封装,如下图。

Interface模型编辑

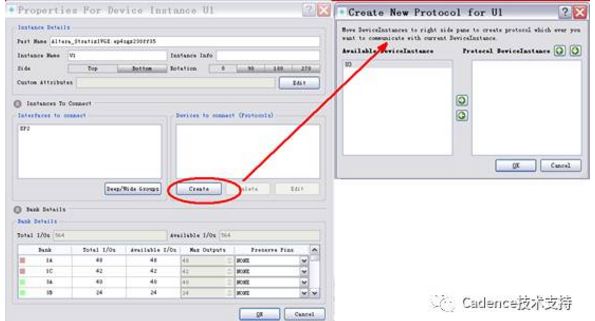

(2)实现FPGA之间的互连:右击FPGA,选择Instance Properties命令,弹出的对话框中,Interface ToConnect栏显示Interface和该FPGA的连接关系,Devices to connect(Protocol)栏中显示的是FPGA之间的连接关系。

点击Create,在Create New Protocol对话框中,选择与U1(FPGA)相连的另一个FPGA(U3)。

FPGA之间的连接关系创建

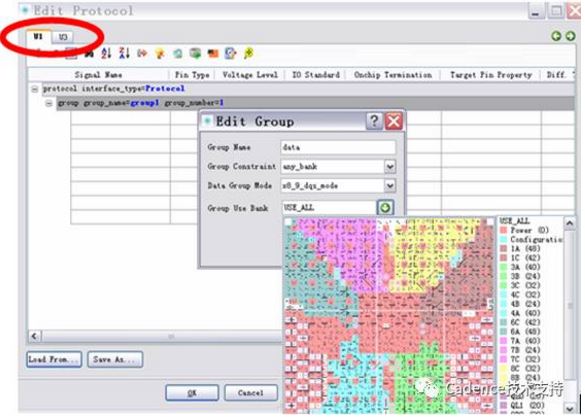

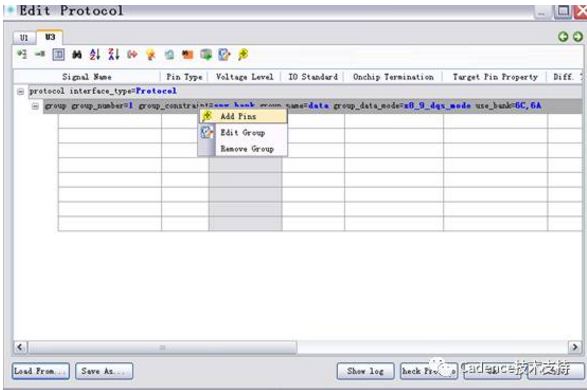

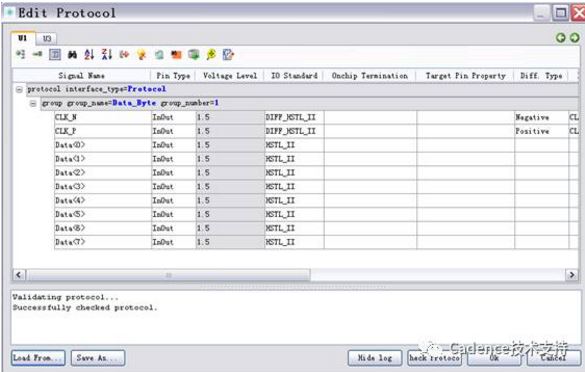

然后,点击OK之后,弹出Edit Protocol对话框,既可以编辑FPGA之间的连接关系与规则设置,如下图8-10。

图8:FPGA连接关系规则设置与引脚区域分配

图9:编辑FPGA之间的引脚连接关系

图10:完成FPGA连接关系的设置,即完成protocol连接设置

点击OK即可完成FPGA之间的连接关系设定,以及相应规则与区域设置。

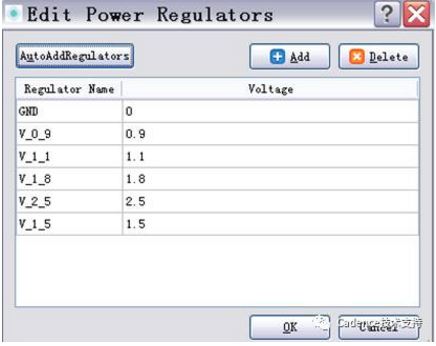

(3)配置FPGA电源、地引脚

执行Tools/Define Power Regulators编辑系统设计中的电源、地配置,如下图。

电源配置

然后执行Tools/Map Power Connections可以分配电源、地的连接关系,再执行CheckPower Connection进行电源、地网络的检查。

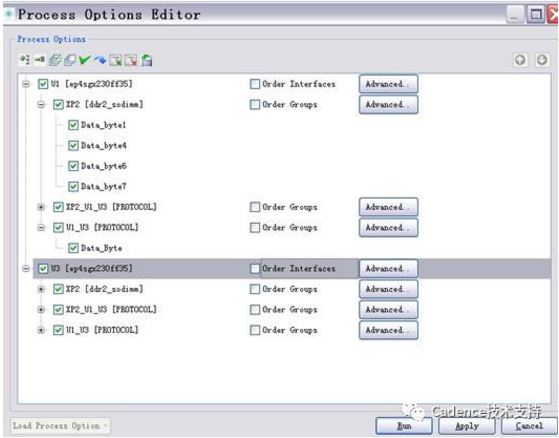

(4)完成之前的网络连接关系设置后,执行Tools/Run Design,就可以在FSP中运行网络连接关系配置了,如下图:

运行FSP连接关系

指定运行连接关系配置的器件

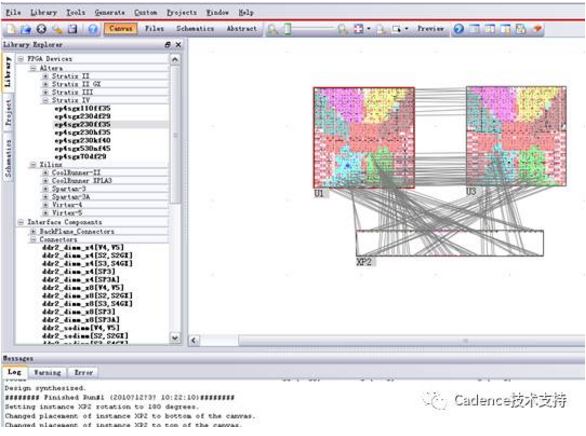

(5)运行完成后,就会在FSP的设计界面中,显示出设置完成的连接关系

运行FSP,完成系统级网络连接

下期:我们将介绍如何将FSP中的设计转换成原理图,并将其生成对应的布局信息。

如您还需其他Cadence技术资料或销售需求,请联系info@eegle.com.cn或致电4007-188-616与我们联系

|