|

在PCB设计中规则设置是必不可少的,它也可以被称为DRC检查规则,用来确定电路板的走线规则是否符合设计要求。在Allegro PCB的电路板设计过程中,设计约束规则主要包括时序规则、走线规则、间距规则、信号完整性规则等以及物理规则等设置。

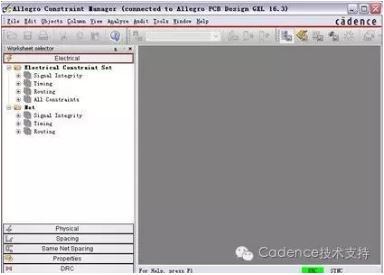

首先,需要认识一下,Allegro PCB的约束管理器:在PCB设计界面中,执行Setup/ Constraints/Constraint Manager命令,弹出Allegro Constraint Manager 对话框,如下图。

在约束管理器中,设计者可以对电路板的电气规则、物理规则、间距规则等设计规则进行设置定义。约束规则可以按板层、网络或者区域进行设置。

约束管理器是Cadence系统提供的专用规则设置系统,主要有菜单栏、工具栏、工作表选择区、工作状态报告栏四部分,在工作表中选择一个对象,然后右击,在弹出的命令菜单中,可以进行任意操作。

工作表选择区内可以选择电气规则、物理规则、间距规则等规则设置。在对应Net文件夹内,可以创建指定网络的对象分组,如:系统、设计、总线、差分对、扩展网络(XNet)、网络、相对或匹配群组,也可以创建基于相关属性的电气规则(ECSet)、物理规则(PCSet)、间距规则(SCSet)等。

约束管理器的约束对象分为引脚对、总线和匹配群组,她们相互之间存在优先级差异,即底层对象会集成顶层对象指定约束,为底层对象指定的约束优先高于上层继承的约束,对象层次的优先级为系统、设计、总线、差分对、扩展网络、相对或匹配群组、引脚对。

一、电气规则设置

在约束管理器中,选择Electrical选项卡,其中可以为设计或网络来设置时序规则、信号完整性规则、布线的电气规则(延时、差分对)等,执行Objects/Create/Electrical CSet命令可新建电气规则。

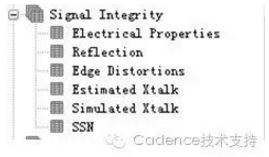

1、选择信号完整性仿真规则Signal Integrity属性,其中包括电气属性、反射属性、单调失真属性、初始串扰、仿真串扰以及同步开关噪声这六个规则设置。

其中各项规则设置如下:

(1)、电气属性设置(Electrical Properties)包括下列内容的设置:Frequency表示网络频率;Period表示网络周期;Duty cycle表示占空比;Jitter表示时钟抖动值;Cycle to measure表示仿真时测量周期;Offset表示补偿值;Bit Pattern表示仿真输出的位格式。

(2)反射属性设置(Reflection)包括以下内容的设置:

Overshoot表示过冲设置;Noise margin表示噪声的补偿裕量。

(3)失真属性(Edge Distortions)包括以下内容设置:

Edge Sensitivity表示网络或扩展接收端的单调敏感性能;First incident Switch 表示第一个波形的转换设置。

(4)初始串扰设置(Estimated Xtalk)包括以下内容设置:Active window表示网络处于转换或产生噪声的窗口;Sensitive window表示网络处于稳态和易受干扰的状态窗口;Ignore nets表示计算串扰时可忽略的网络;Xtalk的max栏表示网络允许最大窜扰值;Peak xtalk的max栏表示一个干扰网络对受扰网络产生的最大允许串扰。

(5)仿真串扰设置(Simulated Xtalk)包括以下内容设置:该项内容与初始串扰设置内容相同,用以查看仿真后的串扰结果,初始串扰设置则是用以预测串扰结果。

(6)同步开关噪声设置(SSN)包括以下内容设置:Max SSN表示最大同步开关噪声;Power bus name表示电源总线名称;Ground bus name表示地总线名称;Actual表示实际噪声;Margin表示噪声裕量,若是负值则会产生冲突。

2、选择时序规则设置(Timing):

时序设置包括以下两个工作表设置,Switch/Settle Delays用以设置第一个转换延时(Min First Switch)和最后的建立延时(Max Final Settle),通过仿真对实际值和约束值进行比较,可得出裕量值;Setup/Hold则用以设置时钟网络名称、时钟周期、时钟延时和时钟偏移量,将这些数值进行比较,能够得出系统是否符合要求。

3、电气走线规则设置(Routing):

(1)连线规则设置(Wiring)包括以下内容设置:Topology用以选择走线拓扑结构,有菊花链、星形等结构;Stub length用以设置走线较大短桩长度;Exposed length用以设置表层走线较大长度;Parallel用以设置并行走线的线宽和线距约束;Layer Sets用以设置走线板层。

(2)过孔规则设置(Vias)包括以下内容设置:用以检查网络过孔数量限制(Via Count)和过孔尺寸是否符合要求(Match Vias)。

(3)阻抗设置(Impedance)包括以下内容设置:Single-line Impedance用以设置目标网络的阻抗和偏差设置,通过计算可以得出阻抗的实际值和裕量,注意叠层和材料的设置必须正确,结果才能准确。

(4)走线最大/最小传输延时设置(Min/Max Propagation Delay)包括以下内容设置:Pin Pairs栏有以下三项设置,Longest/Shortest Pin Pair表示将最小延时赋予最短引脚,最大延时约束赋予最长引脚;Longest/Shortest Driver/Receiver表示将最小延时赋予最短驱动/接收端引脚对,最大延时赋予最长驱动/接收端引脚对;All Drivers/All Receivers表示将最大、最小延时约束赋予所有的驱动/接收端引脚对。Prop Delay则用以设置走线最大和最小延时。

(5)走线的最大和最小长度设置(Total Etch Length):用以设置走线最大和最小长度,并可以显示实际的曼哈顿比例,可以计算走线的不耦合长度。

(6)差分对走线设置(Differential Pair)包括以下内容设置:Uncoupled length用以设置差分对耦合长度的设置,其中Gather Control设置耦合带控制,Ignore表示忽略差分对刚从芯片出来时候的不耦合长度,忽略耦合带,Include表示差分对走线长度包含耦合带长度;Phase tolerance用以设置差分对相位偏量;Min Line Spacing用以设置差分对的最小线间距;Coupling Parameters用以设置差分对的耦合参数,其中Primary width表示差分对理想线宽,Primary gap表示差分对理想线间距,Neck width用以设置差分对最小线宽,Neck gap表示差分对最小允许线间距,Tolerance表示允许的偏差。

(7)相对延时设置(Relative Propagation Delay)包括以下内容设置:选择这个选项卡时,设计者可以将多网络设置成匹配群组,对匹配群组则需要设置相对延时。

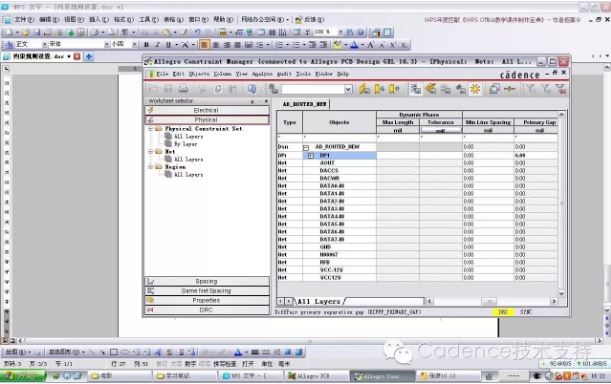

选择Physical选项卡,则可以对电路板设计的物理规则进行设置,如下图所示:

二、物理规则设置

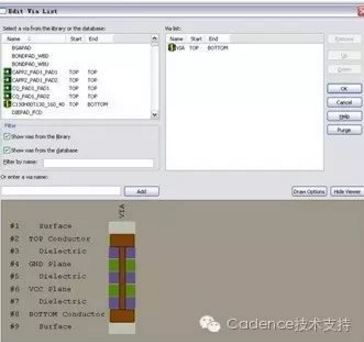

执行Objects/Create/Physical CSet命令可以新建物理规则,然后可以设置走线的物理约束。其中走线约束与电气规则中的意思相仿,不再赘述了,然后还有需要设置的:Vias可设置过孔类型,BB Via Stagger用以设置埋/盲孔的过孔间距,Allow用以设置焊盘过孔连接方式。此外,点击网络对应Vias设置栏,在弹出Edit Via List对话框,则可以对每个网络进行相应的过孔设置选择正确的过孔焊盘,如下图。

三、间距规则设置

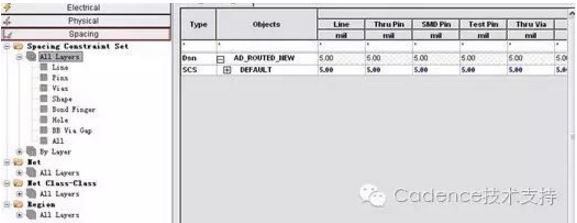

电路板上的导线并非完全绝缘的,会受到工作环境的影响,产生不利于PCB正常工作的因素,因此需要规定导线之间的间距。同样,非导线元件之间要正常工作也需要设置安全距离,间距规则设置界面如下图。

选择约束管理器的Spacing选项卡,则可以对系统或网络进行间距规则的设置,执行Objects/Create/Spacing

CSet即可新建间距规则。

在间距规则设置中,可以设置走线间距、走线与过孔间距等PCB设计中的各种间距规则。

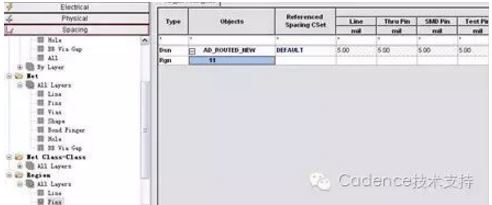

四、区域规则设置

在电路板设计中,有时一个网络会从宽松区域走线至密集区域,这个网络就有可能需要进行区域的局部规则设置,包括间距规则和物理规则,这样才能让走线在某些特殊区域自动转换走线规则。

区域规则设置的方法如下:

在约束管理器中,点击Region选项卡,执行Objects/Create/Region命令创建区域规则,如下图建立区域规则11所示,并可对新建区域规则进行设置:

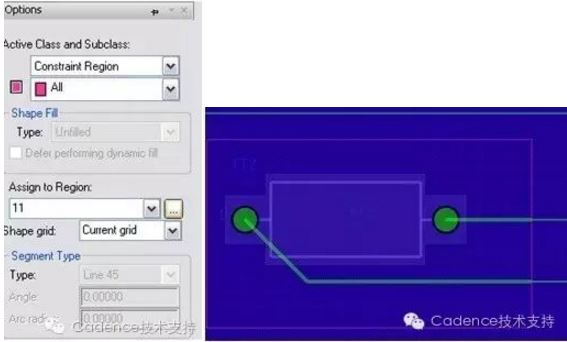

1、在PCB设计界面中,执行Shape/Rectangle命令,在Options对话框中选择Constraint Region类和需要区域规则的板层,并将该Shape赋予对应的区域规则如下图,这样网络走线经过该区域时就会自动改变走线规则,有利于密集区域走线。

在Allegro PCB设计中,Cadence自带的约束管理器集成了各种PCB设计规则,便于规则的设置与管理,有助于设计者更好的进行规则管理设计。只要能正确进行约束管理设置,就能更好的将电路板设计出来。

以上就是Cadence Constraint Manager约束规则设置的全部内容啦,下周我们还会有更精彩的小窍门与大家分享哦~~~

|