|

核心优势

● 确保供电可靠

● 降低成本,减少延误,预防现场故障

● 为封装和电路板提供可靠的压降分析

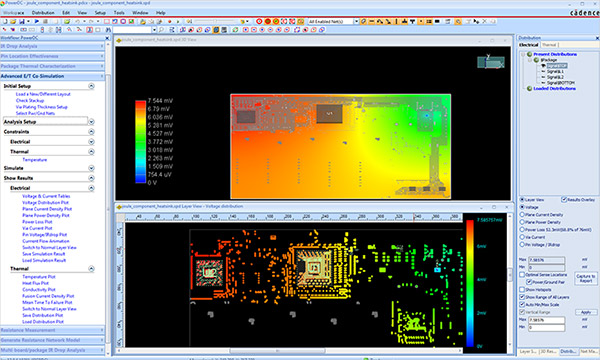

To ensure you achieve reliable power delivery, Cadence® Sigrity™ PowerDC™ technology provides efficient DC analysis for signoff of IC package and PCB designs, including electrical/thermal co-simulation to maximize accuracy. PowerDC technology quickly pinpoints excessive IR drop, along with areas of excess current density and thermal hotspots to minimize your design’s risk of field failure.

为确保您获得可靠的供电,Cadence® Sigrity™ PowerDC™技术可为IC封装和PCB设计签收提供高效的包含电/热协同仿真在内的直流分析,大限度地提高设计精准度。PowerDC技术可快速查明压降过大、电流过密、和温度过高的区域,大限度地降低设计的现场故障风险。

主要功能

● 使用在设计早期的原理图阶段获取的PowerTree™数据(source/sink定义),自动设置DC仿真

● 识别难以定位的高阻抗窄线位置,在成千上万过孔中精确定位会在运行时失败的过孔

● 确定是否可能在不增加DC或热可靠性风险的情况下减少电路板的层数

● 对多板PCB,以及带芯片级信息的封装设计进行评估

● 具有独特框图结果视图等一系列可视化选项的What-if改进选项

● 易于部署的工作流程,新手用户和专家均可轻松掌握

● 专利认证的自动化功能,可确定较佳感应线位置

● 高度精确,即使对于具有多种电压区域和复杂平面结构的复杂设计也同样表现出色

● 全面支持多结构设计,包括堆叠式芯片、多板以及所有常用封装类型

● 使用PowerTree数据可视化原理图的电源部分

● 使用PowerTree数据运行不含铜的预布局仿真,选择符合设计标准的元器件

● 优化了 Cadence SiP Layout, Allegro® Package Designer, 和 Allegro PCB Designer 流程

● 轻松应用于Mentor、Zuken和Altium流程,支持混合CAD数据库,满足多结构设计

|