|

对近乎完美的追求是永无止境的,电子设计领域便是好的例证。20年前,我们从未想过只要发出命令,客厅里的灯便能点亮;但是现在,智能家居技术已经让声控灯成为我们的日常。

然而,要使这样的技术不断发展,则需要电子设计的不断进步来实现“近乎完美”;智能家居中的印刷电路板技术其实已经历多年的发展与完善。

为了满足这些器件的高级计算需求,密集PCB设计中需要高速电路。特别需要注意的是这些器件的RF部分,在增加电路板功能性的同时也大大增加了电路板的复杂性。为了实现成功设计,PCB设计人员需要平衡电路板上高速PCB布线与RF PCB布线的要求。本文将讨论如何实现这一平衡。

当开始设计同时具有高速和RF电路的印刷电路板时,我们必须遵守许多特定的高速设计规则。但是无论如何,我们设计的都是“电路板”:这意味着,除了将使用的新设计参数之外,我们还必须遵循PCB设计的所有常规规则。包括:

-

可制造性设计(DFM)规则,包括为组装和测试设计电路板(DFA & DFT):如果我们的设计因为违反了基本的可制造性设计规则而不能继续构建,我们将面临更大的问题。

-

数字、模拟、电源和混合信号技术的基本PCB设计规则:仅仅因为我们需要更多空间用于高速走线或RF屏蔽,并不意味着我们可以忽略常规的PCB设计间距规则而将设计挤在一起。

-

发热器件的散热问题:高速电路往往会产生更多的热量,所以我们比以往都更需要注意散热问题,需要确保我们的电路板得到了应有的冷却处理。

现在,我们的PCB设计已经完成设置,且已经为高速和RF PCB布线的附加规则和约束做好了准备。让我们来看看高速和RF PCB布线技术的关键点。

对于智能家居、移动或其他物联网设备,尺寸通常是设计中的一个重要因素。由于高速电路的电路板尺寸较小,我们需要相应地进行规划,以确保留有所需的空间。某些高速布线可能需要特定的走线宽度来适应指定的欧姆值以及额外的间距来尽量减少串扰。

布置高速和RF电路时,需要确保放置的位置符合原理图中布置的信号路径。高速电路依赖于信号路径中引脚之间的短直接走线,而且我们不希望这些走线在连接之前在电路板上徘徊。另一方面,大数据和内存总线需要长度相等,这通常意味着其中一些线路必须加长。在这种情况下,我们需要分配出足够的空间来将测量的走线长度调整到正确的值。

另一个考虑因素是电源和接地网的正确layout。一些器件需要放置在专用电源或接地平面区域,以将其噪声与敏感的高速布线隔离开来。我们还需要在IC的每个电源引脚旁边放置旁路电容器,并使其尽可能靠近。另一个关键问题是确保高速传输线路不会穿过电源和接地平面分裂布线。这些走线需要一个连续的平面作为返回路径,分裂则会产生一个无法穿越的峡谷。这会导致EMI问题,从而破坏设计的信号完整性性能。

RF布线为我们的走线方式引入了一整套全新的要求。为了创建正确的大小和形状,一些走线拓扑结构将与我们所习惯的非常不同。我们还需增加额外的过孔来屏蔽和增加宽度和空间,所有这些都需要更多的空间。高速和RF设计的另一个方面是它们的板层叠构。精确配置叠构中的层和材料来支持高速和RF微带和带状线布线非常重要。

带有调整走线的3D高速布线

高速和RF PCB布线是否成功取决于许多因素。其中包括遵守高速layout指南,以便正确布线高速和RF PCB走线长度。如何预先规划RF PCB布线以及简单地设计电路板的基本电路(如:如何在电路中连接继电器<微信内部链接>)也很重要。接下来我们详细介绍一下。

为了让我们的高速或RF电路板设计按预期运行,布线必须根据下面列出的特定参数进行:

为了在PCB设计上成功布线高速和RF电路,我们需要遵循一些基本准则,帮助我们避免常见问题。首先,确保我们的原理图包含足够的信息,以帮助layout人员进行布线。其次,精确了解高速或RF设计需要什么样的材料和层叠结构,以便关键的设计数据(如走线宽度和间距)不会在layout中发生变化。器件布置也需要精确,以便产生短而直接的信号路径,而高速走线需要遵循旨在创建较佳信号完整性性能的拓扑模式。

高速和RF走线对于电路板的较佳信号完整性性能极其重要。我们需要控制走线宽度以尽量减小走线阻抗容差,同时保持足够的间隔以防止串扰。电源和接地回路必须远离可能中断信号回路的裂缝或空隙,差分对和测量线路必须在其容差范围内。在设计过程中,为了保持良好信号完整性,PCB设计人员最好遵循PCB设计工具的设计规则和约束。

控制长度的走线调整示例

在设计带有高速或RF电路的印刷电路板时,我们最好能够提前规划。首要目标之一是决定什么是正确的板层叠构配置以及将使用什么样的电路板材料。这将便于我们为设计设置正确的阻抗控制走线宽度,从而实现高速传输线的较佳性能。还有许多其他的技巧可以帮助我们进行设计,比如为我们的RF电路提供充分的接地平面、屏蔽和滤波保护。

高速和RF设计的一个真正问题是对设计的非关键领域关注不够。当这种情况发生时,这些非关键领域可能成为电路板其他部分如何运作的真正问题。因此,我们要重视基本的PCB设计技能,即使这些技能就像连接电路中的继电器一样简单。

设计具有高速和RF PCB布线的印刷电路板对任何设计人员来说都是一个挑战。有了标准电路板,我们将有足够的空间和机会来优化器件布置、应对电源分配网络(PDN)挑战以及降低串扰和噪声。

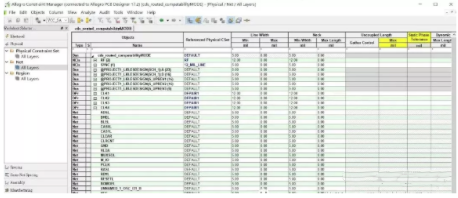

当涉及电路板上的高要求信号时,设计规则检查(DRCs)可以成为我们的帮手。使用正确的PCB设计系统,我们可以创建包含高速和RF设计所需的全部信息的原理图,甚至从一开始就获得叠构的所需信息。

顶级系统同时具备仿真和分析工具,可以在布局前对电路进行建模,在布局后进行分析,从而为设计提供较佳性能。最后,我们需要强大的layout工具。这些工具应具有多种布线功能以及完整的设计规则和约束系统,使我们处于PCB布线技术的顶端。

在Allegro® PCB Designer管理器中,管理高速和RF PCB布线约束十分容易

所幸,对于我们所有从事高速和RF PCB布线项目的人来说,上述PCB设计工具已经唾手可得。Allegro PCB Designer设计软件具有我们需要的全部特性和功能,可以精确地为高速和RF设计进行布线,并可以访问各种不同的布线功能以及新的设计规则和约束系统。

|