|

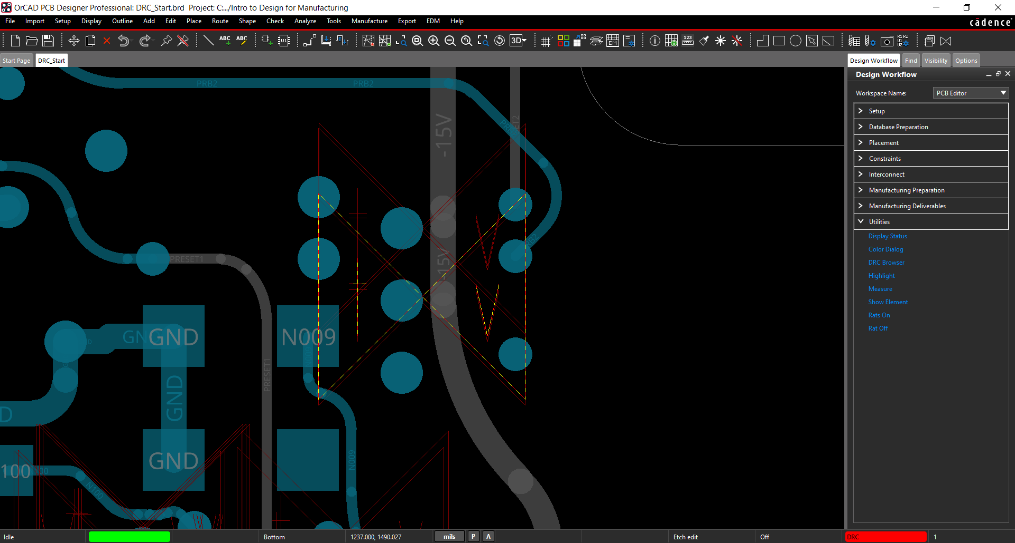

在OrCAD PCB Designer Professional软件中打开“DRC_Start.BRD”设计文件。 在OrCAD PCB Designer Professional软件中打开“DRC_Start.BRD”设计文件。

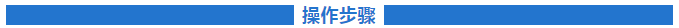

在菜单栏中选择“Tools > DRC Browser”。 在菜单栏中选择“Tools > DRC Browser”。

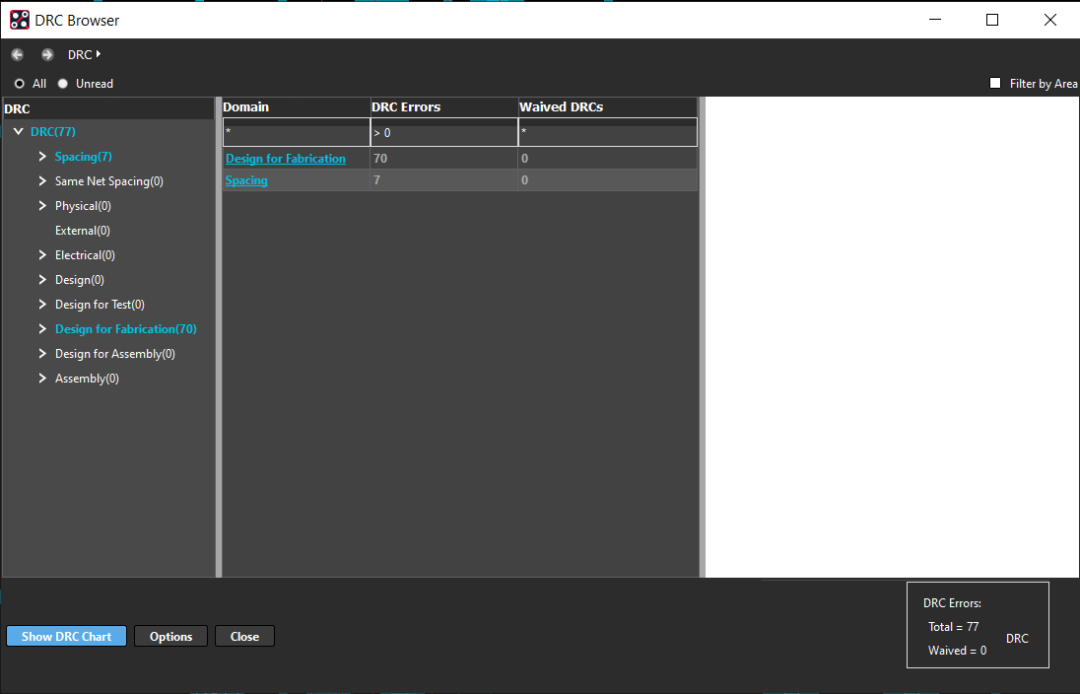

选择“Show DRC Chart”。 选择“Show DRC Chart”。

单击图表中的柱形图以获取更多信息。 单击图表中的柱形图以获取更多信息。

关闭图表并最小化DRC Browser。 关闭图表并最小化DRC Browser。

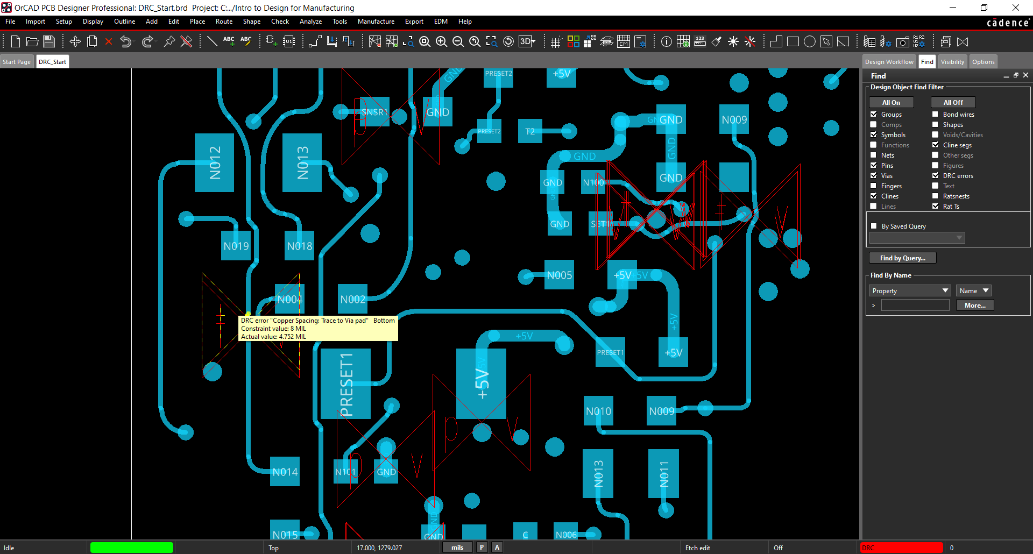

回到PCB设计视窗中,将鼠标悬停在Via21 N004的DRC Marker上。 回到PCB设计视窗中,将鼠标悬停在Via21 N004的DRC Marker上。

注意:查看文本以获得解决DRC Error的附加信息,此错误是由于走线放置得太靠近过孔而造成的。

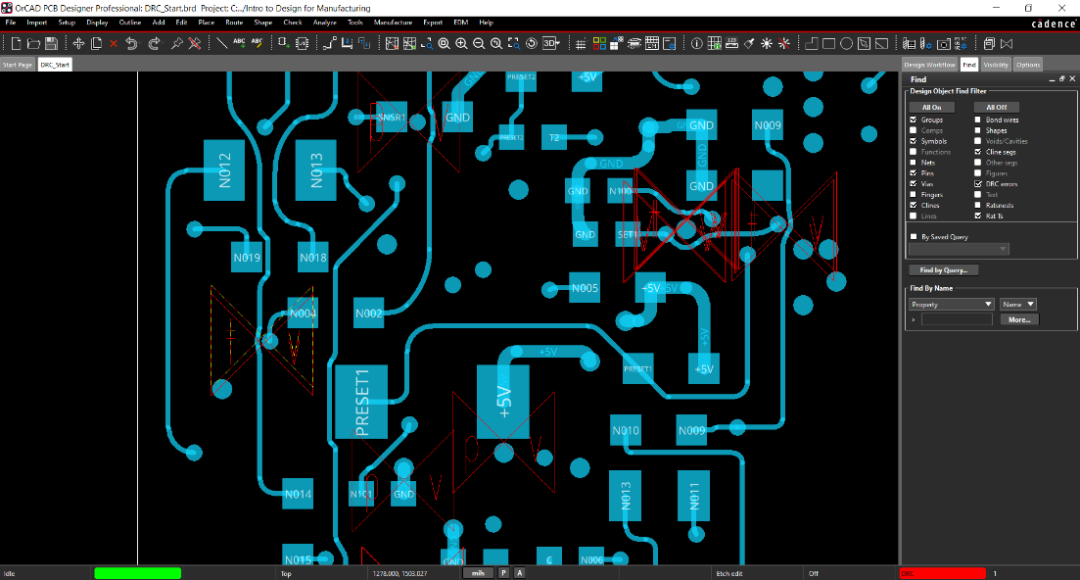

在菜单栏中选择“Setup > Application Mode > Etch Edit“。 在菜单栏中选择“Setup > Application Mode > Etch Edit“。

在Find选单中,取消选择“DRC Error“,以便更容易地选择走线。 在Find选单中,取消选择“DRC Error“,以便更容易地选择走线。

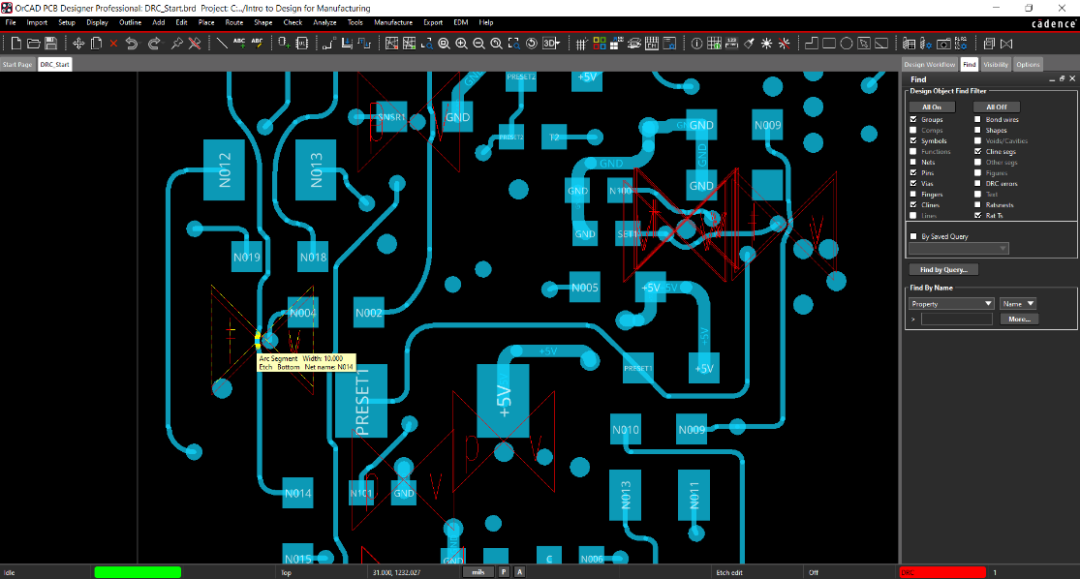

单击引发错误的走线。 单击引发错误的走线。

将走线从过孔处移开,单击放置。 将走线从过孔处移开,单击放置。

注意:此时DRC marker已消失,DRC error已解决。

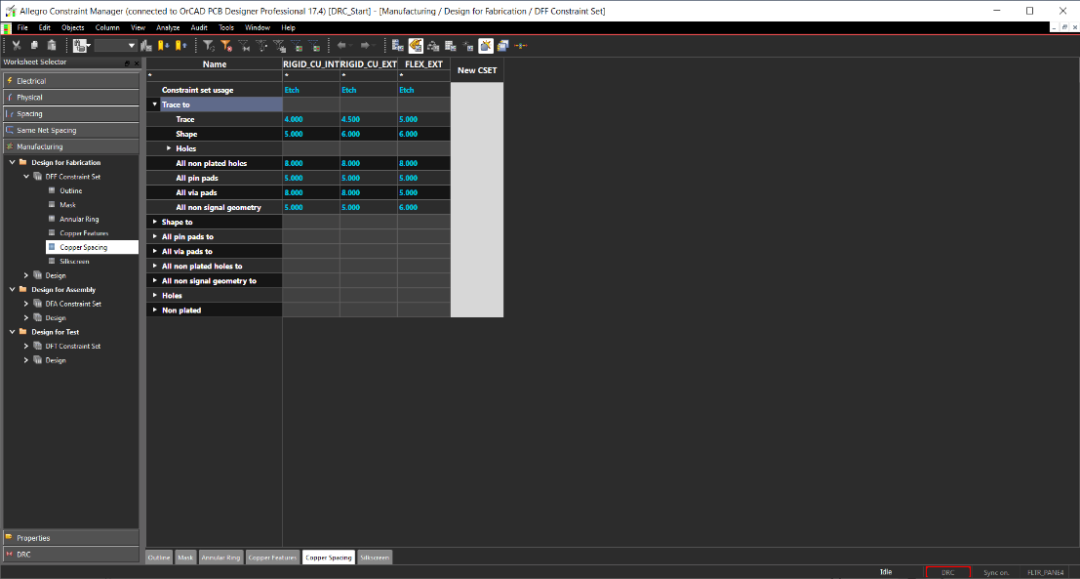

在菜单栏中选择“Setup > Constraints”。 在菜单栏中选择“Setup > Constraints”。

在Worksheet Selector中,选择“Manufacturing > Design for Fabrication > DFF Constraint Set> Copper Spacing”。 在Worksheet Selector中,选择“Manufacturing > Design for Fabrication > DFF Constraint Set> Copper Spacing”。

在“Constraint Set Window”中,展开“Trace To”已查看分配的约束。 在“Constraint Set Window”中,展开“Trace To”已查看分配的约束。

注意:可以在这里管理间距约束,并在多个设计中重用这些约束。为了便于重用,将约束导出到电子表格中:Fileà ExportàConstraints。

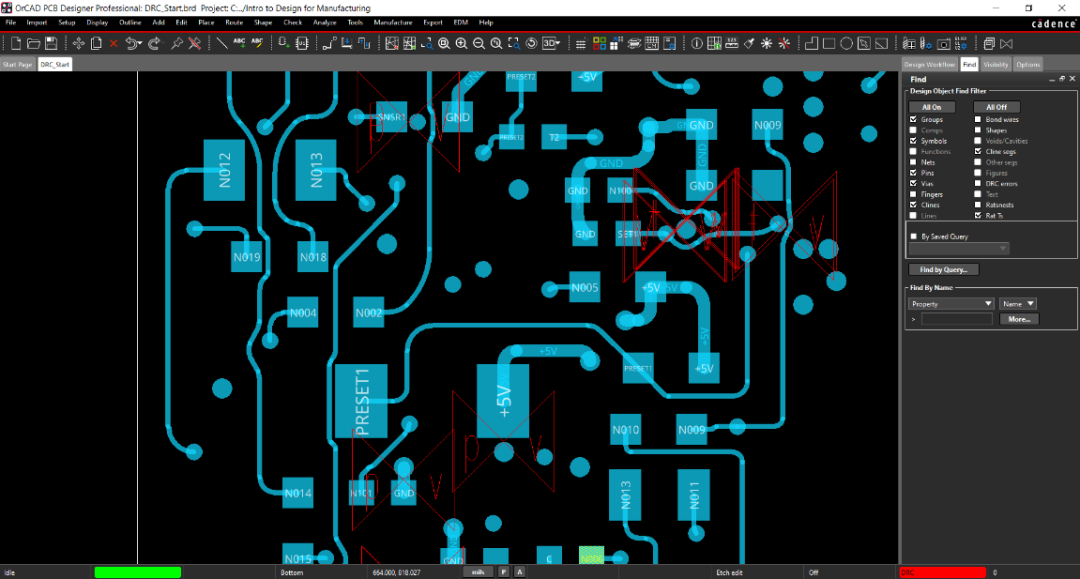

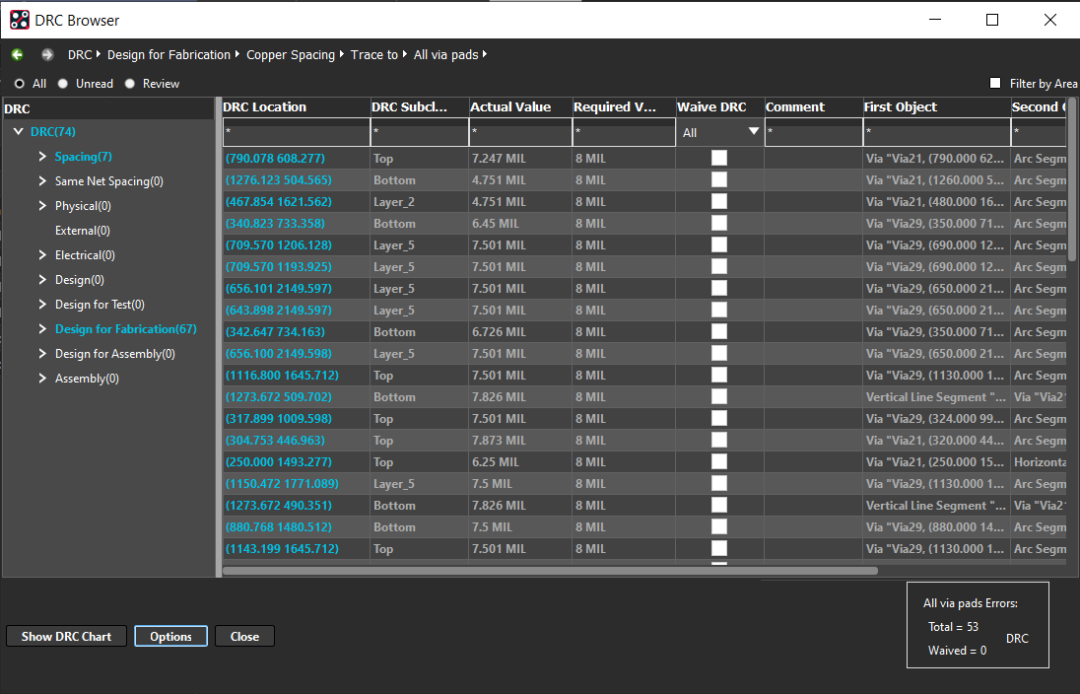

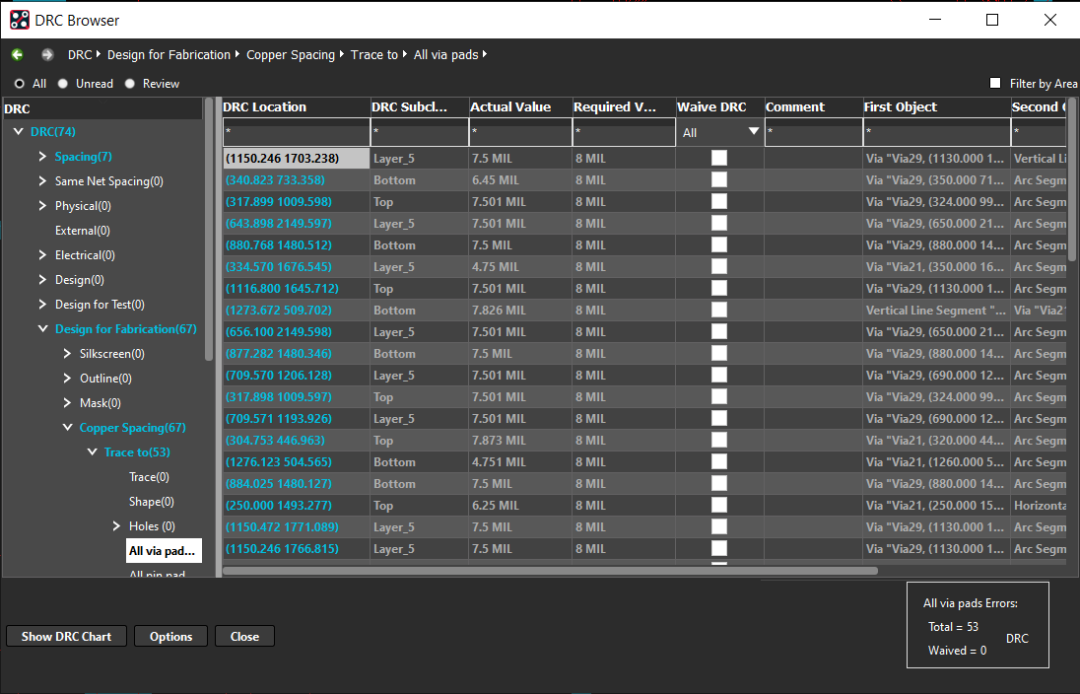

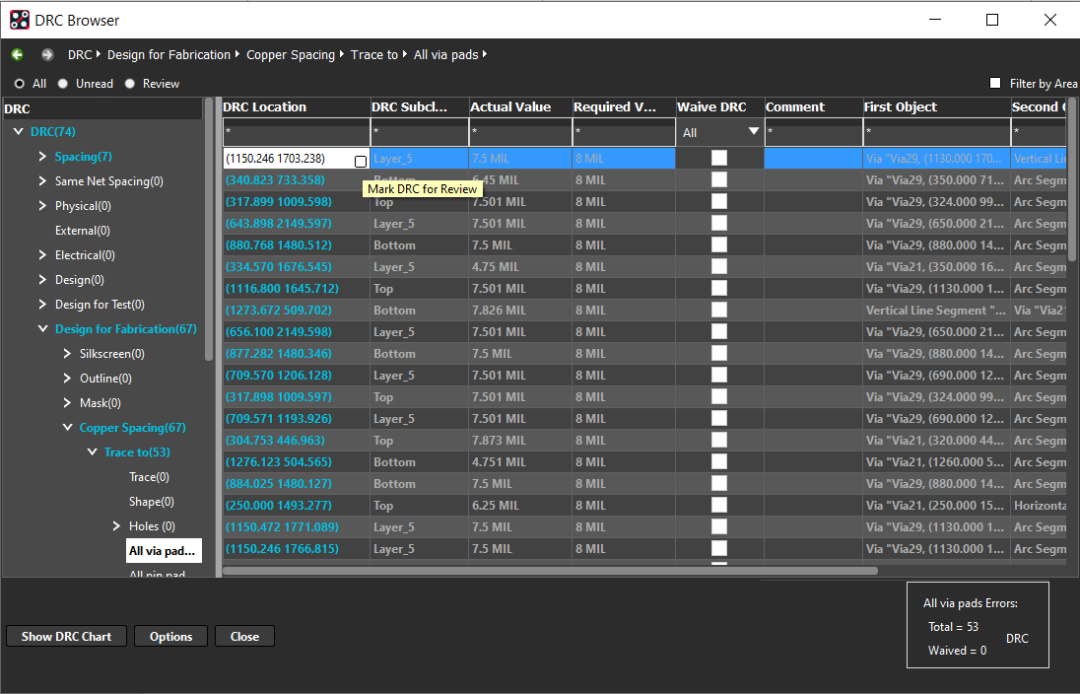

关闭Constraint Manager并打开DRC Browser。浏览到以下路径:DRC > Design for Fabrication > Copper Spacing > Trace to > All via pads。 关闭Constraint Manager并打开DRC Browser。浏览到以下路径:DRC > Design for Fabrication > Copper Spacing > Trace to > All via pads。

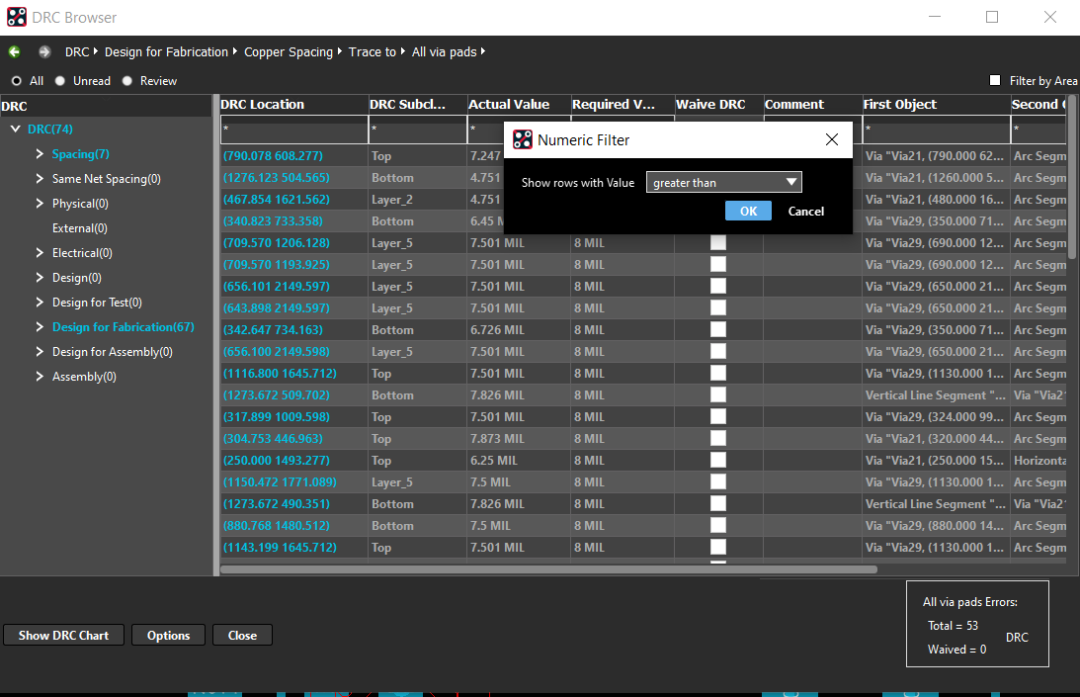

注意:可以通过选择所需列中的星号(*)并选择一个过滤器来筛选DRC errors。

单击DRC Location。 单击DRC Location。

注意:这将带我们到PCB上DRC Marker的位置。当鼠标移到DRC Error上时,在Find Tab中选择DRC Error以查看更多信息。

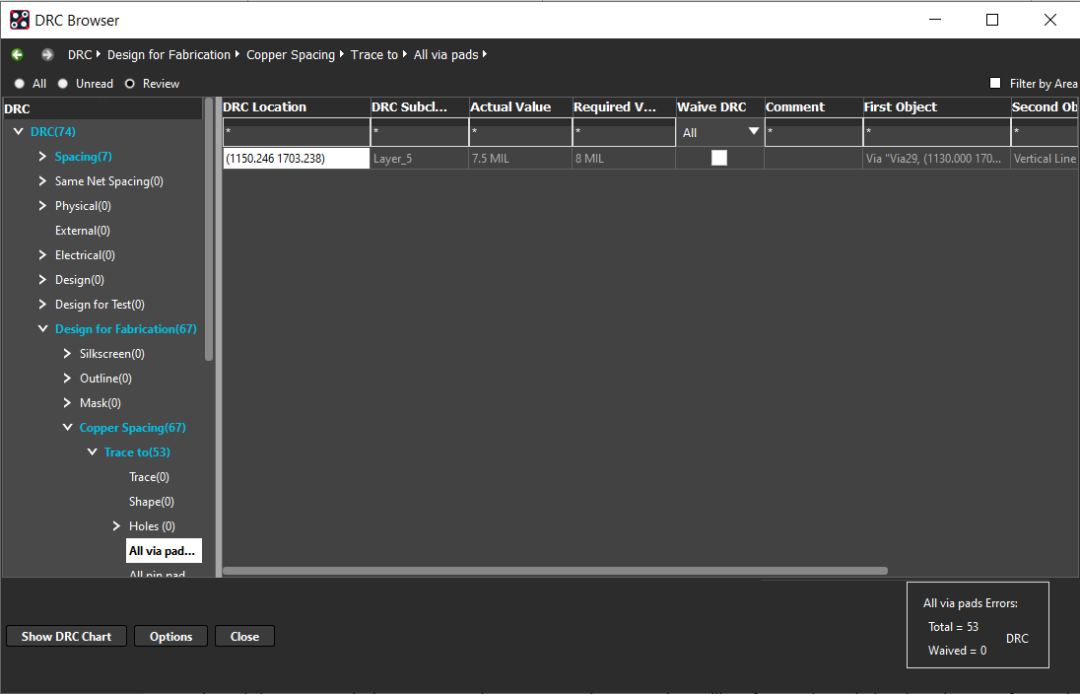

通过勾选DRC Location中对应坐标旁边的复选框来标记错误。 通过勾选DRC Location中对应坐标旁边的复选框来标记错误。

选择Review来查看标记的错误。 选择Review来查看标记的错误。

随着设计工期的不断缩短和设计复杂性的增加,把 DFM 和 DRC 问题交给制造商解决所带来的风险是承受不起的。OrCAD PCB Designer软件可以在设计过程中实时发现任何潜在的制造错误,确保产品性能符合预期,顺利生产。

|