|

据悉,6G的峰值数据速率将实现1000千兆比特/秒,而这一数字是5G的50倍。与5G相比,6G所能带来的绝对不止速度上的提升。能被真实感受到的场景体验、虚拟现实等也或许不再是遥不可及的事情。届时,6G究竟将带来怎样的改变,十分值得期待。

随着6G时代到来,物联网将进化为智联网,这也将会给电子工程师带来非常大的机遇。当前电子工程师的综合素质在普遍提升,除了产品的成本、可靠性、电路板、功能等指标能反应电子工程师一定的能力水平以外,精通英语或者其他的第二外语,善于与人沟通,在一个领域有所建树,对电子行业系统有比较充分的了解,并能持续不断学习也非常重要。

判断PCB工程师的设计水平,就看能否符合如下要求,符合条数越多,设计水平越厉害:

1、功能运行正常;

2、满足EMC测试要求;

3、PCB性价比高;

4、布局、布线整洁美观;

5、设计时间短,工作效率高;

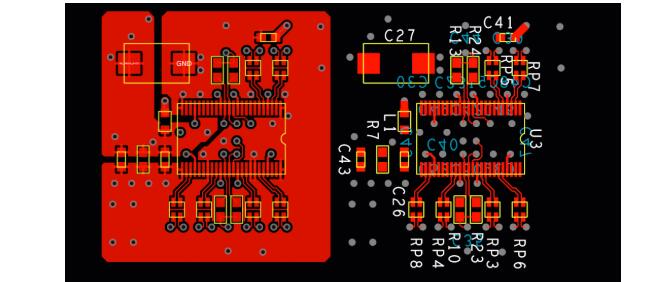

在现代PCB设计中,设计的系统复杂度越来越高,在每次的设计中从零开始的话,势必会增加劳动成本和时间。使用Allegro软件进行PCB Layout设计时,当电路图中有很多路相同的模块,使用复用模块的操作方法,可以显著提高工作效率,同时也可以使PCB布局在整体上显得美观。模块的复用为产品升级,新产品开发,对存在多个相同模块的PCB设计项目提高效率提供了帮助。

复用模块(Reuse Module)是布局中可以重复应用的部分,可以应用在相同的设计上,也可以应用在存在类似电路的不同设计上。非正式的模块可以透过place replicate命令生成,以便快速应用于模块复用的电路设计中。正式的模块通常与电路的电路图相关联,以便在放置过程中加以利用。

为了方便在其它设计中能应用模块,位置复制流程通常是以建库的方式完成。为了维护设计意图和完整性,在 Allegro® SPB 17.4 版本中已对复用模块流程进行了以下增强:

● 在摆放模块时会自动将动态shape转成静态shape

● 模块在复用过程中会被lock,可以通过unlock来解锁

● disable_module_auto_lock:可以通过这个变量阻止模块被lock

● disable_module_shape_convert:可以通过这个变量阻止模块中动态shape变成静态shape

Reuse Module-Only Objects:复用模块独有的对象

复用模块创建过程可能包含比我们要求多的对象,但是这些对象却又包含在设计中。这样就会导致增加创建步骤,或者在将其发布到模块库之前进行一些小的调整时,难以打开生成的模块(.mdd)文件。执行模块文件内的更新可能是棘手的,意外断开全局电源和地引脚或缺少约束规则的约束区域都会使更新变得困难。

为了使在设计之外更容易管理模块(.mdd)文件,需要添加一些额外的数据到模块中,比如铜平面、约束区域和文本注释。这个数据可以标记为模块独有的。在模块应用时不包括这些对象,以避免不必要的或重复的对象被引入到设计中。

可以通过Edit – Property命令在.mdd编辑状态下将MODULE_NO_IMPORT属性添加到对象上。

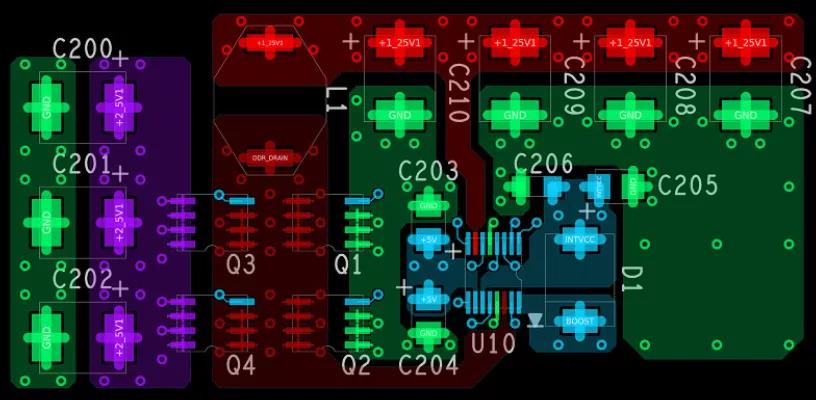

Replace Modules:替换模块

有时同一电路需要不同的变体,以更好地适应它所需要的位置被放置。设计师通常会在所有地方使用相同的复用模块,但是随着摆放位置的变化,一些模组可能需要调整。以便更好地运用到设计中,会用一个变体模块替换现有的复用模块。但是如果需要选择全部零件然后在电路中应用变型组件,这可能会很费时间。

在Allegro SPB 17.4 QIR3版本中,添加了快速替换已经放置的复用模组的功能,可以对所有位置或选中的模块进行替换。

选取复用模块,右键执行Replace Modules, 即可从Design中或Library中选择替换的模块。

Allegro新版本 SPB 17.4 QIR3 已于日前发布,Allegro PCB 部分除了在上文提到的复用模块和在动态铜箔和GPU图形计算持续强化效能之外,更在分析/约束规则、DesignTrue DFM 、3D Canvas和Symphony Team Design 上有不少增强功能。

想要了解更多Allegro 17.4的高级功能吗?欢迎与我们联系。

|