Cadence SPB 22.1版本更新已经有一段时间了,有一部分用户已经正在使用。我们将继续为大家带来SPB 22.1 新增功能的解析,希望可以帮助更多的人了解更新至SPB 22.1后所带来的变化。

接下来将介绍的是22.1版Allegro®System Capture的增强功能和新功能。主要包括:加速原理图设计、Variants流程、系统级设计增强、支持导入.MCM文件 、Library Authoring增强功能、设计完整性中新的审计规则、使用Tcl和Directives进行定制。

// 原理图加速器 //

在处理原理图设计时可以用来提高工作效率的新功能和增强功能。

1、性能优化

在本版本中,对原理图设计的许多方面进行了改进,以提高性能和响应时间,包括以下方面:

■ 打开和保存设计

磁盘上的System Capture设计和库数据现在使用行业标准的压缩-解压缩方法。这使得项目打开、保存、归档和其他相关磁盘IO操作的性能提高了2倍到5倍。

■ 布线性能

交互式布线性能已提高了2倍至5倍,采用了新的结点计算实时算法和改进的数据缓存技术。

■ 画布选择

对于大型原理图中选择操作的性能也提高了3倍至5倍

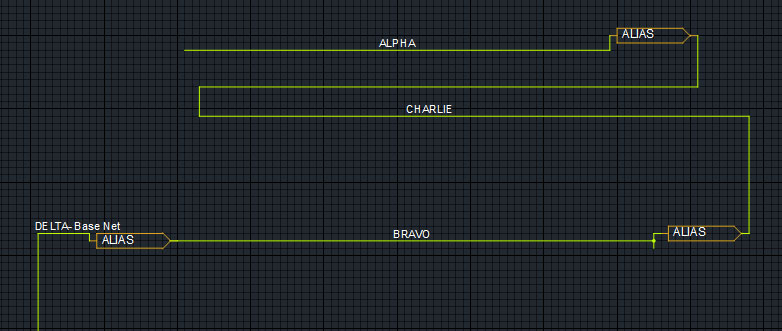

2、显示基础网络标记

当多个网络出现别名时,获胜的网络名称将用作物理名称。现在System Capture可以配置在画布上显示获胜的网络或基本的网络。例如,在下图中,DELTA是基础网络。您在网络名称旁边看到的后缀称为文本覆盖,可以自定义。

要配置此功能,请在site或project的cpm文件的CANVAS部分设置以下指令:

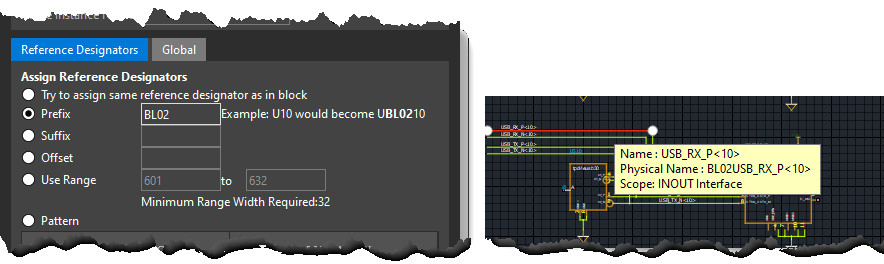

3、扩展物理网名的前缀和后缀

在阶层设计中放置模块时,可以为模块选择一个前缀或后缀。此前缀或后缀现在也应用于单个网络或总线的物理网名称。此功能不需要额外设置。下图分别显示了设置前缀和后缀的效果。

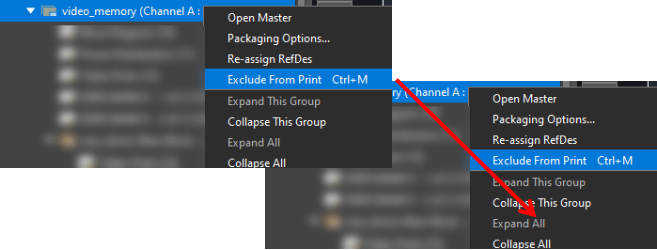

4、支持模块打印

默认情况下,将打印设计中的所有模块和页面。要限制某些模块的打印,请将site.cpm或design文件中的 PRINT_EXCLUSION 指令设置为

PRINT_EXCLUSION 'true'

现在,在模块上单击鼠标右键时,有一个新的选项“Exclude From Print ”可用。选中后,一个图标会显示将不打印该模块。

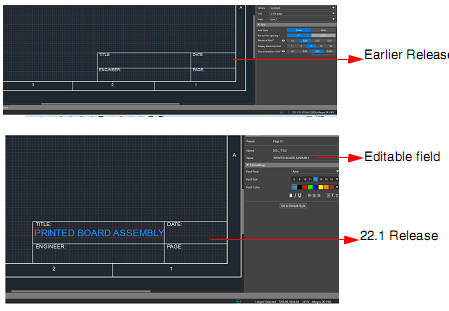

5、支持页面边框上的属性

到目前为止,对于从DE-HDL迁移的设计和从DE-HDLL零件库迁移的页面边框,页面边框上的属性被注释为notes。现在情况发生了变化,这些属性现在作为properties引入。对于页面边框符号上定义的属性占位符,设计者现在也可以更改属性值。但不能改变可见性。下图显示了这种变化:

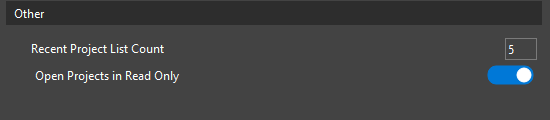

6、以只读方式打开项目

为了避免意外的编辑设计(特别是在团队设计环境中)和避免锁定设计模块或页面,本版本引入了一个新控件。

启用此选项时,即使某些设计对象已被锁定,打开设计时画布上会有一个只读水印,在右上角显示只读状态。如果要启用编辑,请单击Edit Design.

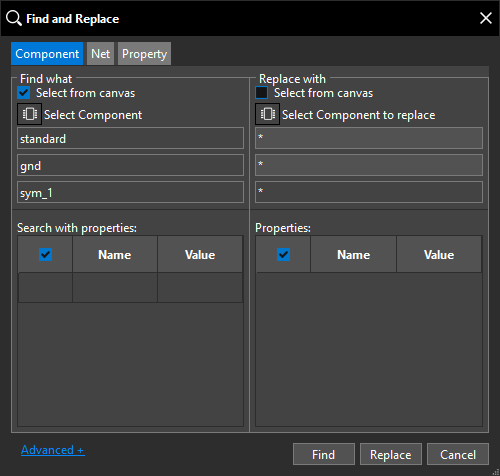

7、查找和替换特殊符号

查找和替换功能现已增强,您可以替换特殊符号,如电源、接地或端口。可以在画布上选择特殊符号,也可以从单击 Component 时打开的Search 窗口中选择特殊符号。

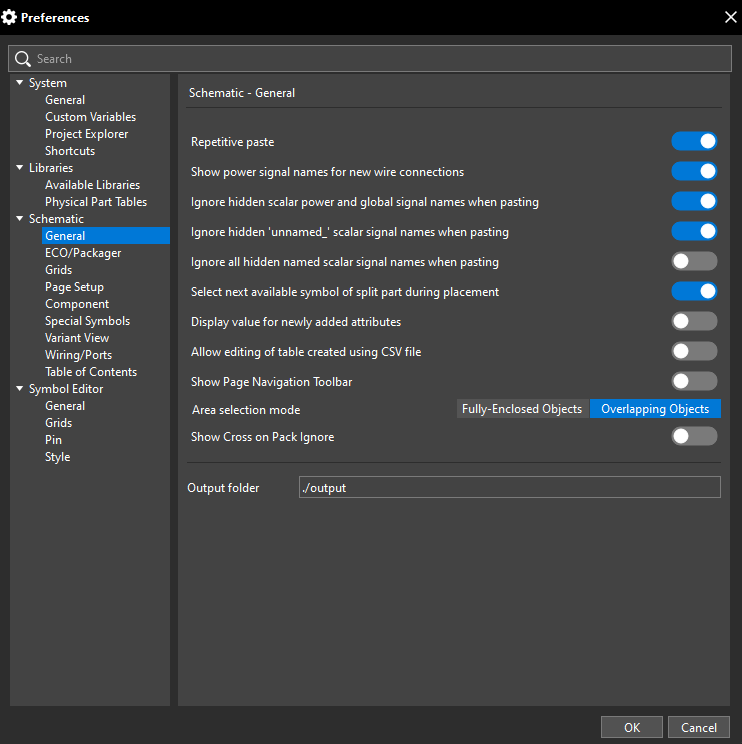

8、控制信号名称的复制和分配

以前,当连接到电源时,信号和电线的名称都会被自动分配和显示。此外,当复制和粘贴电路时,会添加隐藏的信号名称。根据用户反馈,现在可以配置默认行为。控制信号名称显示的指令可以添加到site.cpm或在Preferences窗口中设置。

现在,您可以控制以下内容,并从所见即所得的信号名称显示方式中获益:

● 连接到电源时,在电线上添加或显示信号名称。

● 如果所附的电源没有被复制,则在粘贴选择时转移隐藏的电源信号名称。

● 粘贴选择时转移隐藏的命名和“unnamed_*”信号名称。

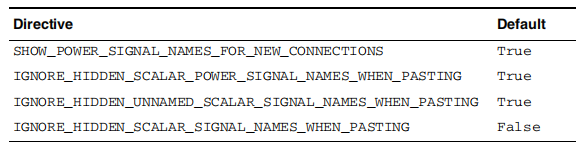

这些选项的相应指令如下:

受这些控制措施影响的操作包括:

● 向电源添加新的连接

● 重命名网络

● 将电源网络接入总线

● 复制没有连接电源的电路

如果未连接电源,则从选择电路中删除电源信号名称

9、保持Reference代号

在早期版本中,复合式零件或分割零件的Reference代号(Ref Des)会随着零件的连续处理而更改。现在,零件的所有部分都作为一个整体被处理,这将使得Ref-Des在Part Manager更新后得以保留。

10、Bus Bits的自动清除

以前,如果阶层模块的接口发生变化,并且接口的bit个数减少,则必须使用Tools – Purge Bus Bits 命令手动清除总线位数。现在,这些总线位数会被自动清除。因此,Tools – Purge Bus Bits 的清除总线位数的命令已被撤销了。

Important

在版本17.4-2019 HotFix 030之后的任何版本中创建或更新的设计完全向后兼容,可以在早期版本中打开。为了避免任何数据的不一致,建议不要在早期版本中编辑设计。但是,如果必须在早期版本中进行修改,请确保在新版本中以修正模式使用runDBDoctor 的Tcl命令。

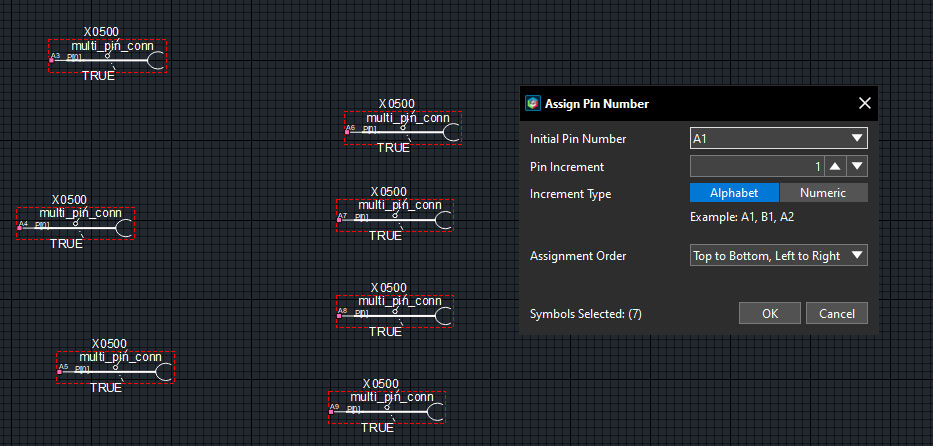

11、分配引脚连接

在处理单引脚的复合式零件时,现在可以在原理图画布上选择一组组件,并根据零件定义(chips.prt)中的数据分配Pin Number。

以上,是关于Allegro®System Capture中原理图加速器的分享,而Variants流程、系统级设计增强、Library Authoring增强功能等方面的内容,我们将在后期继续为您介绍,敬请期待!